U型双极性肖特基势垒场效应晶体管的工艺集成

IF 5.3

2区 材料科学

Q2 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

摘要

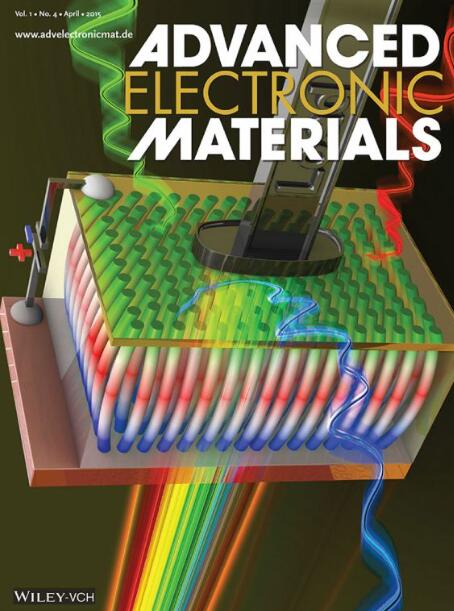

研究具有不同架构的晶体管对于开发高性能、紧凑的器件至关重要,因为它们可以在相同或更小的占地面积内提高集成电路的功能。仿真研究表明,使用U形通道制造的晶体管具有更高的功能,因为其自然几何形状可以实现栅极四面结构和小占地面积内的长通道长度。晶体管的实验实现是探索电路应用的必要条件。本文介绍了U形双极肖特基势垒场效应晶体管的工艺集成路线和首次实验结果。此外,还详细说明了制造3D晶体管的挑战和改进步骤。该器件在p支路和n支路均具有高度对称的导通电流。自对准接触形成和原子力显微镜成像用于简化制造和方便3D结构监测。此外,与传统的3D结构相比,所提出的器件结构中自对准接触的形成大大简化。还进行了TCAD仿真以支持实验结果,并展示了该器件的未来潜力和可扩展性。总之,它有效地解决了制造3D晶体管的挑战,并通过其绝缘体上的硅驱动了器件设计的创新。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Process Integration of U‐Shape Ambipolar Schottky–Barrier Field‐Effect Transistors

Research on transistors with various architectures is crucial for developing high‐performance, compact devices, as they improve the functionality of integrated circuits within the same or smaller footprint. Simulation studies have shown that transistors fabricated using a U‐shape channel have a higher functionality as their natural geometry enables the realization of gate‐all‐around structures and long channel lengths within a small footprint. The experimental realization of the transistor is essential for exploring circuit applications. This paper presents the process integration route and the first experimental results of a U‐shape ambipolar Schottky barrier field effect transistor. Also, a detailed explanation of the challenges in fabricating a 3D transistor and the improvement steps are given. The fabricated device demonstrates highly symmetrical on‐currents for both p‐ and n‐branches. Self‐aligned contact formation and atomic force microscopy imaging are used to simplify fabrication and facilitate 3D structural monitoring. In addition, the formation of self‐aligned contacts in the proposed device architecture is significantly simplified compared to traditional 3D architectures. TCAD simulations are also performed to support the experimental findings and demonstrate the device's future potential and scalability. In conclusion, it effectively addresses the challenges of the fabrication of 3D transistors and drives innovations in device design with its silicon‐on‐insulator body.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Advanced Electronic Materials

NANOSCIENCE & NANOTECHNOLOGYMATERIALS SCIE-MATERIALS SCIENCE, MULTIDISCIPLINARY

CiteScore

11.00

自引率

3.20%

发文量

433

期刊介绍:

Advanced Electronic Materials is an interdisciplinary forum for peer-reviewed, high-quality, high-impact research in the fields of materials science, physics, and engineering of electronic and magnetic materials. It includes research on physics and physical properties of electronic and magnetic materials, spintronics, electronics, device physics and engineering, micro- and nano-electromechanical systems, and organic electronics, in addition to fundamental research.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: