Robust sub-100 nm T-Gate fabrication process using multi-step development

IF 2.8

Q2 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

Abstract

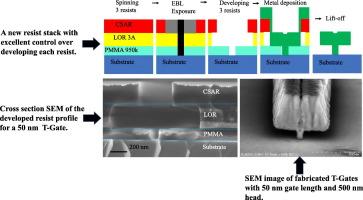

We demonstrate the fabrication of sub-100 nm T-Gate structures using a single electron beam lithography exposure and a tri-layer resist stack - PMMA/LOR/CSAR. Recent developments in modelling resist development were used to design the process, in which each resist is developed separately to optimise the resulting structure. By using a modelling approach and proximity correcting for the full resist stack, we were able to independently vary gate length (50-100 nm) and head size (250-500 nm) at the design stage and fabricate these T-Gates with high yield.

稳健的低于100 纳米 采用多步骤开发的T型门制造工艺

我们展示了使用单电子束光刻曝光和三层抗蚀剂堆叠PMMA/LOR/CSAR制造亚100nm T型栅极结构。抗蚀剂开发模型的最新发展被用于设计工艺,其中每个抗蚀剂都被单独开发,以优化最终的结构。通过对全抗蚀剂堆叠使用建模方法和接近校正,我们能够在设计阶段独立地改变栅极长度(50-100nm)和磁头尺寸(250-500nm),并以高产率制造这些T型门。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Micro and Nano Engineering

Engineering-Electrical and Electronic Engineering

CiteScore

3.30

自引率

0.00%

发文量

67

审稿时长

80 days

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: