Enhancing the Capacitive Memory Window of HZO FeCap Through Nanolaminate Stack Design

IF 5.3

2区 材料科学

Q2 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

Abstract

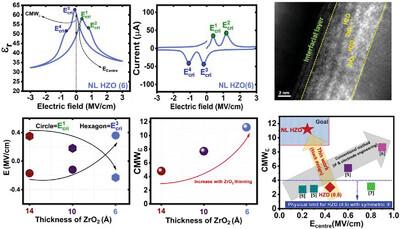

Recently, a capacitive array based on Hf0.5Zr0.5O2 (HZO) has been proposed as an alternative to conventional resistive crossbar arrays for compute-in-memory (CIM). This array operates through a capacitive memory window (CMWε). This arises due to interface asymmetry caused by varying defect densities at the top and bottom interfaces. However, the current CMWε is insufficient, necessitating strategies to enhance it. In this study, the impact of stack design on CMWε is examined and it is demonstrated that it is possible to precisely control critical fields in I–V curves to achieve a significantly higher CMWε. A record high CMWε is achieved through an innovative nanolaminate design. The observed characteristics are explained by the Landau-Ginzburg-Devonshire (LGD) model and the presence of extra critical fields during I–V sweep. The final device exhibits excellent uniformity and high-speed operation. Additionally, a substantial memory window for a non-destructive read operation (NDRO) is confirmed using AC pulses. Alongside detailed electrical characterization, TEM and XRD analyses for an in-depth investigation is employed to uncover the root cause of the superior characteristics achieved. Ultimately, for analog vector-matrix multiplication (VMM) in a capacitive array, the carefully designed nanolaminate stack significantly outperforms HZO (0.5) in both output voltage and voltage swing.

通过纳米叠层设计增强 HZO FeCap 的电容记忆窗口

最近,有人提出了一种基于 Hf0.5Zr0.5O2(HZO)的电容式阵列,作为传统电阻式横条阵列的替代品,用于内存计算(CIM)。这种阵列通过电容式内存窗口 (CMWε) 运行。由于顶部和底部接口的缺陷密度不同,导致接口不对称。然而,目前的 CMWε 并不足够,因此需要采取策略来增强它。本研究考察了堆栈设计对 CMWε 的影响,结果表明可以精确控制 I-V 曲线中的临界场,从而显著提高 CMWε。通过创新的纳米层压板设计,实现了创纪录的高 CMWε。观察到的特性可以用朗道-金兹堡-德文郡(LGD)模型和 I-V 扫频过程中存在的额外临界场来解释。最终器件具有出色的均匀性和高速运行性能。此外,使用交流脉冲还证实了非破坏性读取操作(NDRO)所需的大量存储窗口。除了详细的电气特性分析外,还采用了 TEM 和 XRD 分析进行深入研究,以揭示实现卓越特性的根本原因。最终,对于电容阵列中的模拟矢量矩阵乘法 (VMM),精心设计的纳米叠层在输出电压和电压摆幅方面都明显优于 HZO (0.5)。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Advanced Electronic Materials

NANOSCIENCE & NANOTECHNOLOGYMATERIALS SCIE-MATERIALS SCIENCE, MULTIDISCIPLINARY

CiteScore

11.00

自引率

3.20%

发文量

433

期刊介绍:

Advanced Electronic Materials is an interdisciplinary forum for peer-reviewed, high-quality, high-impact research in the fields of materials science, physics, and engineering of electronic and magnetic materials. It includes research on physics and physical properties of electronic and magnetic materials, spintronics, electronics, device physics and engineering, micro- and nano-electromechanical systems, and organic electronics, in addition to fundamental research.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: