准最大似然PPS估计器的多核硬件实现

IF 1.1

4区 计算机科学

Q4 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 1

摘要

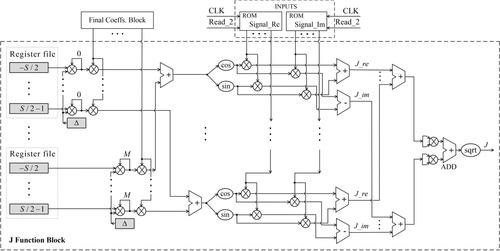

本研究提出了准最大似然算法作为最先进的多项式相位信号(PPS)估计器的多核硬件实现。开发的多时钟周期实现适用于实时实现。为了证明这一点,所提出的设计是在现场可编程门阵列电路上实现的。硬件实现在被各种高斯噪声破坏的PPS上进行了测试和验证。将获得的结果与软件仿真进行比较,表明所提出的基于系统的输出和基于软件的输出之间具有良好的匹配性。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Multi-core hardware realisation of the quasi maximum likelihood PPS estimator

Multi-core hardware realisation of the quasi maximum likelihood algorithm as the state-of-the-art estimator of polynomial phase signals (PPSs) is proposed in this study. Developed multiple-clock-cycle realisation is suitable for real-time implementation. To prove this, the proposed design is implemented on a field programmable gate array circuit. The hardware realisation is tested and verified on PPSs corrupted with various amounts of the Gaussian noise. Obtained results are compared with software simulations showing excellent match between the proposed system-based and the software-based outputs.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

IET Computers and Digital Techniques

工程技术-计算机:理论方法

CiteScore

3.50

自引率

0.00%

发文量

12

审稿时长

>12 weeks

期刊介绍:

IET Computers & Digital Techniques publishes technical papers describing recent research and development work in all aspects of digital system-on-chip design and test of electronic and embedded systems, including the development of design automation tools (methodologies, algorithms and architectures). Papers based on the problems associated with the scaling down of CMOS technology are particularly welcome. It is aimed at researchers, engineers and educators in the fields of computer and digital systems design and test.

The key subject areas of interest are:

Design Methods and Tools: CAD/EDA tools, hardware description languages, high-level and architectural synthesis, hardware/software co-design, platform-based design, 3D stacking and circuit design, system on-chip architectures and IP cores, embedded systems, logic synthesis, low-power design and power optimisation.

Simulation, Test and Validation: electrical and timing simulation, simulation based verification, hardware/software co-simulation and validation, mixed-domain technology modelling and simulation, post-silicon validation, power analysis and estimation, interconnect modelling and signal integrity analysis, hardware trust and security, design-for-testability, embedded core testing, system-on-chip testing, on-line testing, automatic test generation and delay testing, low-power testing, reliability, fault modelling and fault tolerance.

Processor and System Architectures: many-core systems, general-purpose and application specific processors, computational arithmetic for DSP applications, arithmetic and logic units, cache memories, memory management, co-processors and accelerators, systems and networks on chip, embedded cores, platforms, multiprocessors, distributed systems, communication protocols and low-power issues.

Configurable Computing: embedded cores, FPGAs, rapid prototyping, adaptive computing, evolvable and statically and dynamically reconfigurable and reprogrammable systems, reconfigurable hardware.

Design for variability, power and aging: design methods for variability, power and aging aware design, memories, FPGAs, IP components, 3D stacking, energy harvesting.

Case Studies: emerging applications, applications in industrial designs, and design frameworks.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: