倾斜结构的短通道二维场效应管

IF 8.2

2区 材料科学

Q1 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

摘要

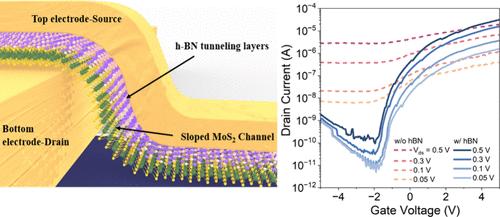

电子器件的小型化仍然是半导体工业的主要焦点,因为它直接影响到性能的提高和成本的降低。然而,实现极端缩小通常依赖于高分辨率光刻技术,这受到复杂性和密集处理时间的限制。二维过渡金属二硫族化合物(2D TMDCs)由于其原子薄的性质和高的杨氏模量,在短通道场效应晶体管(fet)中具有很大的发展潜力。在这里,在二维tmdc FET中,纳米尺度的通道长度是通过构建不使用光刻技术的倾斜结构来实现的。利用h-BN隧道层可确保减轻短信道效应(SCE),从而实现高开关比和低亚阈值摆幅(SS)。这种倾斜结构的短通道FET (SSFET)的通断比超过105,SS为160 mV/dec,导通电流水平为3.70 μA。这种新方法为实现纳米级场效应管提供了一条创新的途径,而无需复杂的制造工艺。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Short Channel 2D FET with Sloped Architecture

The miniaturization of electronic devices remains a primary focus in the semiconductor industry as it directly impacts both performance enhancement and cost reduction. However, achieving extreme scaling down often relies on high-resolution lithography techniques, which are limited by complexity and an intensive processing time. Two-dimensional transition metal dichalcogenides (2D TMDCs) have great potential for developing short-channel field effect transistors (FETs) due to their atomically thin nature and high Young’s modulus. Here, the nanometer-scale channel length in a 2D TMDC-based FET is realized by constructing the sloped architecture without lithography techniques. Utilizing h-BN tunneling layers ensures the mitigated short channel effect (SCE), resulting in a high on-off ratio and low subthreshold swing (SS). This sloped architecture short channel FET (SSFET) exhibits an on–off ratio over 105 with an SS of 160 mV/dec and an on-current level of 3.70 μA. This new approach can provide an innovative pathway to realize the nanometer-scale FET without complicating fabrication processes.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

ACS Applied Materials & Interfaces

工程技术-材料科学:综合

CiteScore

16.00

自引率

6.30%

发文量

4978

审稿时长

1.8 months

期刊介绍:

ACS Applied Materials & Interfaces is a leading interdisciplinary journal that brings together chemists, engineers, physicists, and biologists to explore the development and utilization of newly-discovered materials and interfacial processes for specific applications. Our journal has experienced remarkable growth since its establishment in 2009, both in terms of the number of articles published and the impact of the research showcased. We are proud to foster a truly global community, with the majority of published articles originating from outside the United States, reflecting the rapid growth of applied research worldwide.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: