一种具有异质结和缓冲层的新型双沟栅4H-SiC LDMOS,可提高单事件烧蚀耐受性

IF 1.9

3区 工程技术

Q3 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

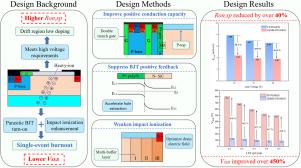

作为重要的航天动力器件,碳化硅(SiC)横向扩散金属氧化物半导体(LDMOS)暴露在空间辐射下容易发生单事件烧坏(SEB),造成灾难性的破坏。本文采用Sentaurus TCAD模拟,提出了1.2 kv 4H-SiC LDMOS的SEB硬化方法。提出了一种低比导通电阻(Ron,sp)的双沟槽栅极4H-SiC LDMOS,显著提高了器件的SEB阈值电压(VSEB)。提出的硬化设计集成了多缓冲层和异质结,令人印象深刻地减轻了漏极区域的高电场,同时抑制了寄生双极结晶体管(BJT)。此外,通过设计双沟槽栅极和扩流层(CSL),器件电阻显著降低。因此,与传统的4H-SiC LDMOS相比,该器件的VSEB提高了(498±11)%,而Ron,sp降低了(41.8±1.8)%。这大大提高了器件在辐射环境中的可靠性。本文章由计算机程序翻译,如有差异,请以英文原文为准。

A new double-trench gate 4H-SiC LDMOS with heterojunction and buffer layer for improved single-event burnout tolerance

As an important aerospace power device, silicon carbide (SiC) Lateral Diffused Metal Oxide Semiconductor (LDMOS) is susceptible to single-event burnout (SEB), which causes catastrophic damage when exposed to space radiation. The current work employs the Sentaurus TCAD simulations to present the SEB hardening method for a 1.2-kV 4H-SiC LDMOS. A double-trench gate 4H-SiC LDMOS containing low specific on-resistance () is proposed, significantly improving the device’s SEB threshold voltage (). The proposed hardening design integrates multi-buffer layer with a heterojunction, impressively mitigating the high electric field at the drain area while suppressing the parasitic bipolar junction transistor (BJT). Besides, the device’s resistance is significantly decreased by designing the double-trench gate and current spreading layer (CSL). Accordingly, the constructed device achieves a (498 ± 11)% increase in while reducing the by (41.8 ± 1.8)% compared with the traditional 4H-SiC LDMOS. This significantly enhances the device’s reliability in radiation environments.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Microelectronics Journal

工程技术-工程:电子与电气

CiteScore

4.00

自引率

27.30%

发文量

222

审稿时长

43 days

期刊介绍:

Published since 1969, the Microelectronics Journal is an international forum for the dissemination of research and applications of microelectronic systems, circuits, and emerging technologies. Papers published in the Microelectronics Journal have undergone peer review to ensure originality, relevance, and timeliness. The journal thus provides a worldwide, regular, and comprehensive update on microelectronic circuits and systems.

The Microelectronics Journal invites papers describing significant research and applications in all of the areas listed below. Comprehensive review/survey papers covering recent developments will also be considered. The Microelectronics Journal covers circuits and systems. This topic includes but is not limited to: Analog, digital, mixed, and RF circuits and related design methodologies; Logic, architectural, and system level synthesis; Testing, design for testability, built-in self-test; Area, power, and thermal analysis and design; Mixed-domain simulation and design; Embedded systems; Non-von Neumann computing and related technologies and circuits; Design and test of high complexity systems integration; SoC, NoC, SIP, and NIP design and test; 3-D integration design and analysis; Emerging device technologies and circuits, such as FinFETs, SETs, spintronics, SFQ, MTJ, etc.

Application aspects such as signal and image processing including circuits for cryptography, sensors, and actuators including sensor networks, reliability and quality issues, and economic models are also welcome.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: