二维晶体管的栅极堆栈工程

IF 40.9

1区 工程技术

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

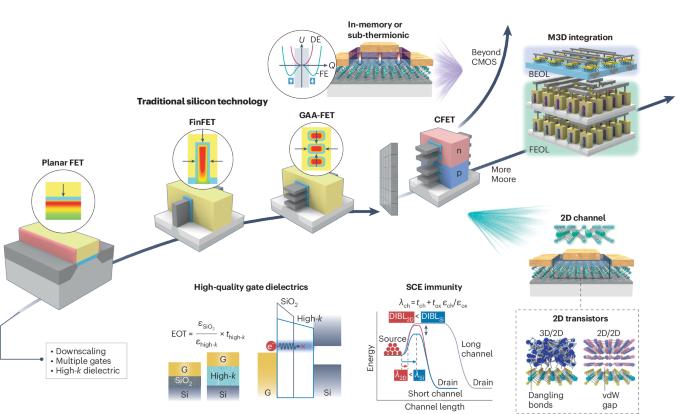

栅极堆栈工程有助于在硅互补金属氧化物半导体技术中实现积极的器件缩放。二维(2D)材料是下一代电子产品中硅的潜在替代品。然而,由于缺乏兼容的电介质和制造方法,用这种材料制造能够有效可靠地控制通道的栅极堆栈本身就具有挑战性。本文探讨了二维晶体管栅极堆栈工程技术的发展。我们将二维金属氧化物半导体栅极堆栈的关键性能指标与当前的硅基技术以及器件和系统国际路线图设定的目标进行基准测试。我们还强调了铁电嵌入式栅极堆栈的最新进展,它提供了额外的功能,可以用于开发高速非易失性存储器和逻辑存储器器件,以及低功耗晶体管。最后,我们考虑了开发基于二维晶体管的先进电子技术需要解决的技术挑战。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Gate stack engineering of two-dimensional transistors

Gate stack engineering has helped enable aggressive device scaling in silicon complementary metal–oxide–semiconductor technology. Two-dimensional (2D) materials are a potential replacement for silicon in next-generation electronics. However, creating gate stacks that are capable of effective and reliable channel control with such materials is inherently challenging owing to the lack of compatible dielectrics and fabrication methods. Here we explore the development of gate stack engineering technologies for two-dimensional transistors. We benchmark key performance metrics for two-dimensional metal–oxide–semiconductor gate stacks against current silicon-based technologies, as well as the targets set by the International Roadmap for Devices and Systems. We also highlight recent advances in ferroelectric-embedded gate stacks, which offer additional functionalities and could be of use in the development of high-speed non-volatile memories and logic-in-memory devices, as well as low-power transistors. Finally, we consider the technical challenges that need to be addressed to develop advanced electronic technologies based on two-dimensional transistors. This Review examines the development of gate stack engineering technologies for two-dimensional (2D) transistors, benchmarking key performance metrics for such gate stacks against current silicon-based technologies and exploring the challenges that need to be addressed in order to create advanced electronic technologies based on 2D transistors.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Nature Electronics

Engineering-Electrical and Electronic Engineering

CiteScore

47.50

自引率

2.30%

发文量

159

期刊介绍:

Nature Electronics is a comprehensive journal that publishes both fundamental and applied research in the field of electronics. It encompasses a wide range of topics, including the study of new phenomena and devices, the design and construction of electronic circuits, and the practical applications of electronics. In addition, the journal explores the commercial and industrial aspects of electronics research.

The primary focus of Nature Electronics is on the development of technology and its potential impact on society. The journal incorporates the contributions of scientists, engineers, and industry professionals, offering a platform for their research findings. Moreover, Nature Electronics provides insightful commentary, thorough reviews, and analysis of the key issues that shape the field, as well as the technologies that are reshaping society.

Like all journals within the prestigious Nature brand, Nature Electronics upholds the highest standards of quality. It maintains a dedicated team of professional editors and follows a fair and rigorous peer-review process. The journal also ensures impeccable copy-editing and production, enabling swift publication. Additionally, Nature Electronics prides itself on its editorial independence, ensuring unbiased and impartial reporting.

In summary, Nature Electronics is a leading journal that publishes cutting-edge research in electronics. With its multidisciplinary approach and commitment to excellence, the journal serves as a valuable resource for scientists, engineers, and industry professionals seeking to stay at the forefront of advancements in the field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: