栅极长度为10nm的间隔设计的GS SOI n-FinFET的性能增强

IF 3.1

4区 工程技术

Q2 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

本研究展示了传统SOI n-FinFET器件的改进,结合了高k间隔和栅极堆栈(GS)工程,栅极长度为10 nm。对三种FinFET结构进行了比较,仿真结果表明,该结构在模拟性能和射频性能方面都有显著改善。模拟参数如ION/IOFF比增加了近104倍,亚阈值摆幅减少了约60%;跨导提高了~ 92%,QF提高了~ 382%,TGF提高了~ 302%,固有增益提高了近8倍,早期电压提高了近5倍,表明该器件适用于高性能CMOS电路。此外,使用截止频率、GFP、TFP等参数进行射频分析,表明所提出的配置有相当大的改进。因此,栅极堆叠和间隔层工程显著提高了FinFET的性能,增强了半导体器件的模拟和射频能力,以实现更高效的集成电路。本文章由计算机程序翻译,如有差异,请以英文原文为准。

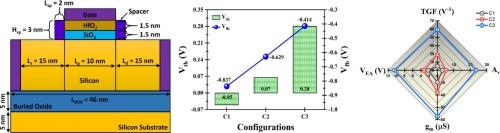

Performance enhancement of a spacer-engineered GS SOI n-FinFET with 10 nm gate length

This study showcases the improvement in conventional SOI n-FinFET devices with the incorporation of a high-K spacer and gate stack (GS) engineering at 10 nm gate length. Three FinFET configurations were considered for comparison, and the simulated results show significant improvements in the analog and RF performance of the proposed configuration. Analog parameters such as the ION/IOFF ratio increased almost 104 times, subthreshold swing reduced by ∼60 %; transconductance increased by ∼92 %, QF improved by ∼382 %, TGF enhanced by ∼302 %, intrinsic gain increased by almost 8 times, and early voltage by almost 5 times, indicating the proposed device is suitable for high-performance CMOS circuits. Further, the RF analysis is performed with parameters like cut-off frequency, GFP, TFP, etc., exhibiting considerable improvement for the proposed configuration. Thus, gate stacking and spacer engineering significantly improve the FinFET performance, enhancing the analog and RF capabilities of semiconductor devices for more efficient integrated circuits.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Microelectronic Engineering

工程技术-工程:电子与电气

CiteScore

5.30

自引率

4.30%

发文量

131

审稿时长

29 days

期刊介绍:

Microelectronic Engineering is the premier nanoprocessing, and nanotechnology journal focusing on fabrication of electronic, photonic, bioelectronic, electromechanic and fluidic devices and systems, and their applications in the broad areas of electronics, photonics, energy, life sciences, and environment. It covers also the expanding interdisciplinary field of "more than Moore" and "beyond Moore" integrated nanoelectronics / photonics and micro-/nano-/bio-systems. Through its unique mixture of peer-reviewed articles, reviews, accelerated publications, short and Technical notes, and the latest research news on key developments, Microelectronic Engineering provides comprehensive coverage of this exciting, interdisciplinary and dynamic new field for researchers in academia and professionals in industry.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: