一种基于忆阻器的快速可重构内存排序系统

IF 40.9

1区 工程技术

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

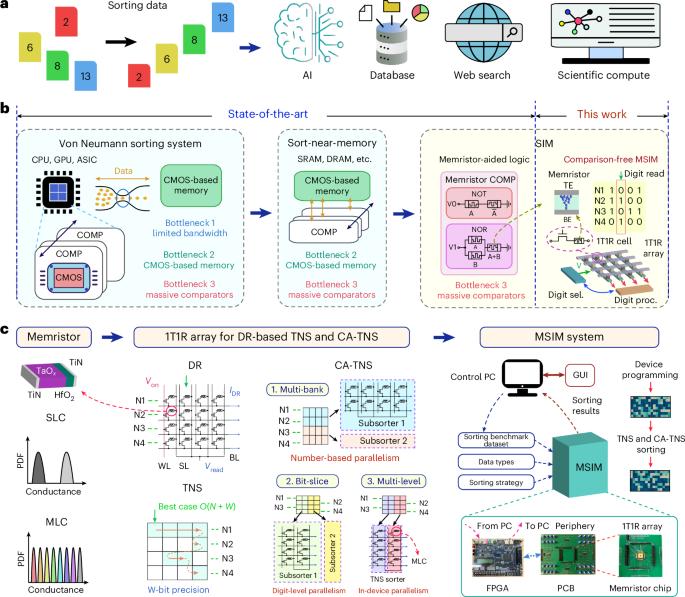

排序是现代计算系统中的一项基本任务。硬件分选器通常基于冯·诺依曼架构,其性能受到数据传输带宽和CMOS存储器的限制。使用忆阻器在内存中进行排序可以帮助克服这些限制,但是当前的系统仍然依赖比较操作,因此排序性能仍然有限。在这里,我们描述了一个快速和可重构的内存排序系统,它使用一晶体管一电阻忆阻器阵列的数字读取。我们开发了支持多种数据量和数据类型的数字读树节点跳过。我们将此方法扩展为跨阵列树节点跳过的多银行、位片和多级策略。实验表明,与传统的分类系统相比,我们的无比较内存排序系统可以提高吞吐量×7.70,能源效率×160.4和面积效率×32.46。为了说明该方法解决实际排序任务的潜力,以及它与其他内存中计算方案的兼容性,我们将其应用于Dijkstra的最短路径搜索和具有原位修剪的神经网络推理。本文章由计算机程序翻译,如有差异,请以英文原文为准。

A fast and reconfigurable sort-in-memory system based on memristors

Sorting is a fundamental task in modern computing systems. Hardware sorters are typically based on the von Neumann architecture, and their performance is limited by the data transfer bandwidth and CMOS memory. Sort-in-memory using memristors could help overcome these limitations, but current systems still rely on comparison operations so that sorting performance remains limited. Here we describe a fast and reconfigurable sort-in-memory system that uses digit reads of one-transistor–one-resistor memristor arrays. We develop digit-read tree node skipping, which supports various data quantities and data types. We extend this approach with the multi-bank, bit-slice and multi-level strategies for cross-array tree node skipping. We experimentally show that our comparison-free sort-in-memory system can improve throughput by ×7.70, energy efficiency by ×160.4 and area efficiency by ×32.46 compared with conventional sorting systems. To illustrate the potential of the approach to solve practical sorting tasks, as well as its compatibility with other compute-in-memory schemes, we apply it to Dijkstra’s shortest path search and neural network inference with in situ pruning. A sort-in-memory system that relies on digit reads on one-transistor–one-resistor memristor arrays can offer improved throughput, energy efficiency and area efficiency compared with conventional sorting systems.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Nature Electronics

Engineering-Electrical and Electronic Engineering

CiteScore

47.50

自引率

2.30%

发文量

159

期刊介绍:

Nature Electronics is a comprehensive journal that publishes both fundamental and applied research in the field of electronics. It encompasses a wide range of topics, including the study of new phenomena and devices, the design and construction of electronic circuits, and the practical applications of electronics. In addition, the journal explores the commercial and industrial aspects of electronics research.

The primary focus of Nature Electronics is on the development of technology and its potential impact on society. The journal incorporates the contributions of scientists, engineers, and industry professionals, offering a platform for their research findings. Moreover, Nature Electronics provides insightful commentary, thorough reviews, and analysis of the key issues that shape the field, as well as the technologies that are reshaping society.

Like all journals within the prestigious Nature brand, Nature Electronics upholds the highest standards of quality. It maintains a dedicated team of professional editors and follows a fair and rigorous peer-review process. The journal also ensures impeccable copy-editing and production, enabling swift publication. Additionally, Nature Electronics prides itself on its editorial independence, ensuring unbiased and impartial reporting.

In summary, Nature Electronics is a leading journal that publishes cutting-edge research in electronics. With its multidisciplinary approach and commitment to excellence, the journal serves as a valuable resource for scientists, engineers, and industry professionals seeking to stay at the forefront of advancements in the field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: