一种用于量子计算机的实时、可扩展、快速和资源高效的解码器

IF 33.7

1区 工程技术

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

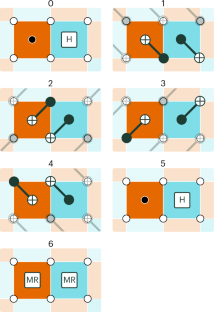

量子计算机的发展将需要仔细管理与量子比特性能相关的噪声效应。然而,负责诊断噪声引起的计算错误的解码器必须有效地利用资源,以实现大量子位计数和低温操作。它们还必须以高速运行,以避免量子计算机的逻辑时钟速率呈指数级下降。为了克服这些挑战,我们介绍了碰撞聚类解码器,并演示了其在现场可编程门阵列(FPGA)和专用集成电路(ASIC)硬件上的实现。我们使用领先的量子纠错方案(表面代码)模拟逻辑内存实验,并演示兆赫解码速度-匹配快速操作模式的要求,例如超导量子比特-使用FPGA达到881量子比特表面代码,使用ASIC达到1,057量子比特表面代码。ASIC设计占地0.06 mm2,功耗仅为8mw。本文章由计算机程序翻译,如有差异,请以英文原文为准。

A real-time, scalable, fast and resource-efficient decoder for a quantum computer

The development of quantum computers will require the careful management of the noise effects associated with qubit performance. However, the decoders responsible for diagnosing noise-induced computational errors must use resources efficiently to enable scaling to large qubit counts and cryogenic operation. They must also operate at speed, to avoid an exponential slowdown in the logical clock rate of the quantum computer. To overcome these challenges, we introduce the Collision Clustering decoder and demonstrate its implementation on field-programmable gate array (FPGA) and application-specific integrated circuit (ASIC) hardware. We simulate logical memory experiments using the leading quantum error correction scheme (the surface code) and demonstrate megahertz decoding speed—matching the requirements of fast-operating modalities such as superconducting qubits—up to an 881 qubit surface code with the FPGA and 1,057 qubit surface code with the ASIC. The ASIC design occupies 0.06 mm2 and consumes only 8 mW of power. The Collision Clustering decoder is introduced, which requires few logical resources on field-programmable gate array hardware, and low power and area occupation on application-specific integrated circuit hardware, while being performant enough to keep up with the syndrome generation time of a quantum processing unit.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Nature Electronics

Engineering-Electrical and Electronic Engineering

CiteScore

47.50

自引率

2.30%

发文量

159

期刊介绍:

Nature Electronics is a comprehensive journal that publishes both fundamental and applied research in the field of electronics. It encompasses a wide range of topics, including the study of new phenomena and devices, the design and construction of electronic circuits, and the practical applications of electronics. In addition, the journal explores the commercial and industrial aspects of electronics research.

The primary focus of Nature Electronics is on the development of technology and its potential impact on society. The journal incorporates the contributions of scientists, engineers, and industry professionals, offering a platform for their research findings. Moreover, Nature Electronics provides insightful commentary, thorough reviews, and analysis of the key issues that shape the field, as well as the technologies that are reshaping society.

Like all journals within the prestigious Nature brand, Nature Electronics upholds the highest standards of quality. It maintains a dedicated team of professional editors and follows a fair and rigorous peer-review process. The journal also ensures impeccable copy-editing and production, enabling swift publication. Additionally, Nature Electronics prides itself on its editorial independence, ensuring unbiased and impartial reporting.

In summary, Nature Electronics is a leading journal that publishes cutting-edge research in electronics. With its multidisciplinary approach and commitment to excellence, the journal serves as a valuable resource for scientists, engineers, and industry professionals seeking to stay at the forefront of advancements in the field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: