调整 R2R 印刷 SWCNT 薄膜晶体管的阈值电压以实现 4 位 ALU

IF 12.3

1区 材料科学

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

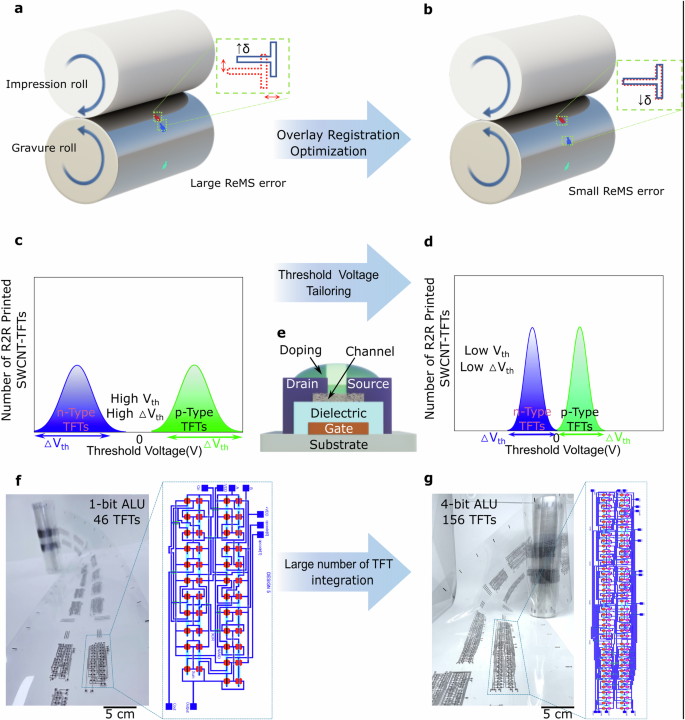

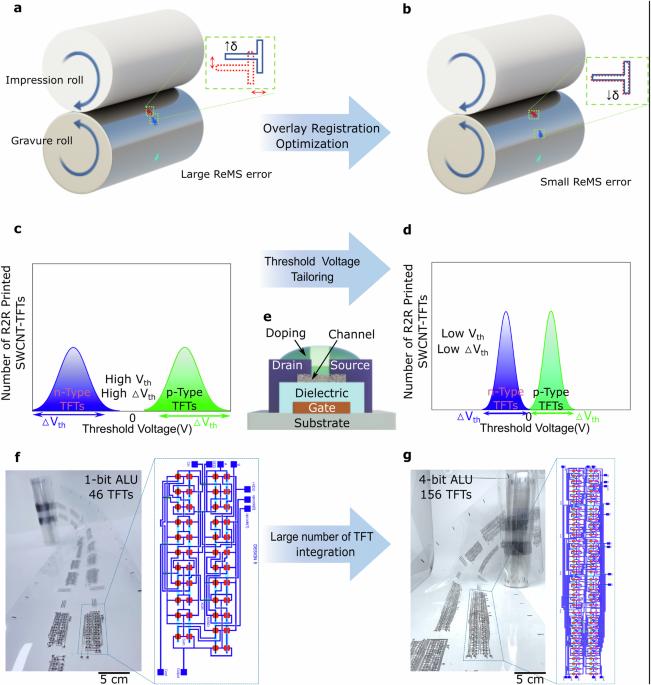

尽管卷对卷(R2R)凹版印刷方法已成为基于 p 型和 n 型单壁碳纳米管薄膜晶体管(p,n-SWCNT-TFTs)制造逻辑电路的另一种可持续技术,但 R2R 印刷的 p,n-SWCNT-TFTs 的阈值电压(Vth > ~8)变化很大,阻碍了互补逻辑电路的集成。在此,我们开发了一种方法,即使用雕刻套准标记的叠加误差最小(< ±40 µm)的第一凹版辊,并使用聚合物基 p 和 n 掺杂油墨实施 R2R 掺杂工艺以定制 Vth,从而缩小了 p、n-SWCNT-TFT 的 Vth 变化。通过这两种方法,印刷在 p、n-SWCNT-TFT 上的 R2R 被定制为将 Vth 值移至接近 ±2.7 V,并将 Vth 值变化降低到 ±1.6 V,同时将噪声裕度提高了 24%,这样就可以集成大量 R2R 印刷逻辑门,并在 ±10 V 工作电压下具有清晰的逻辑电平。基于定制的 p、n-SWCNT-TFT,通过集成 156 个 p、n-SWCNT-TFT,成功演示了完全 R2R 印刷的 4 位算术和逻辑单元。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Tailoring threshold voltage of R2R printed SWCNT thin film transistors for realizing 4 bit ALU

Despite the roll-to-roll (R2R) gravure printing method emerging as an alternative sustainable technology for fabricating logic circuits based on p- and n-types of single-walled carbon nanotube thin film transistors (p,n-SWCNT-TFTs), the wide variation of large threshold voltage (Vth > ~8) in the R2R printed p,n-SWCNT-TFTs prevents the integration of complementary logic circuit. Here, the Vth variation of the p,n-SWCNT-TFTs was narrowed down by developing a method of using the first gravure roll with the minimized superposition error (< ±40 µm) of engraved registration marks and implementing the R2R doping process for tailoring the Vth using polymer-based p- and n-doping inks. Through those two methods, the R2R printed the p,n-SWCNT-TFTs was tailored to shift Vth to near ±2.7 V and reduce Vth variation to ±1.6 V while the noise margin was improved by 24% so that a large number of R2R printed logic gates could be integrated with clear logic levels at ±10 V of operation voltage. Based on the tailored p,n-SWCNT-TFTs, a fully R2R printed 4-bit arithmetic and logic unit was successfully demonstrated by integrating 156 p,n-SWCNT-TFTs.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

npj Flexible Electronics

Multiple-

CiteScore

17.10

自引率

4.80%

发文量

91

审稿时长

6 weeks

期刊介绍:

npj Flexible Electronics is an online-only and open access journal, which publishes high-quality papers related to flexible electronic systems, including plastic electronics and emerging materials, new device design and fabrication technologies, and applications.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: