通过专用且串兼容的密码门为无密码干扰的垂直 NAND 存储铺平道路

IF 8.3

2区 材料科学

Q1 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

摘要

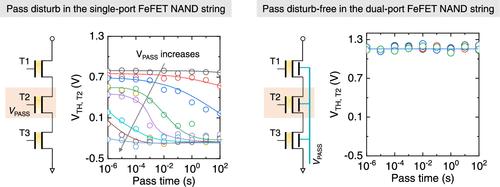

在这项工作中,我们提出了一种双端口单元设计来解决垂直 NAND 存储器中的通路干扰问题,它可以通过一个专用的、与串兼容的通路栅极来传递信号。我们证明了:(i) 通路无干扰特性源于高 VTH(HVT)状态下通路偏置对去极化场的削弱,以及低 VTH(LVT)状态下沟道对应用场的屏蔽;(ii) 双端口设计的模拟和实验证明了 NAND 串中的无干扰运行,克服了单端口设计中的一个关键挑战;(iii) 所提出的设计可以集成到高度缩放的垂直 NAND FeFET 串中,而且通过基底中的全局底部栅极触点,栅极互连的开销可以忽略不计,从而可以将栅极集成到现有的三维(3D)NAND 中。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Paving the Way for Pass Disturb-Free Vertical NAND Storage via a Dedicated and String-Compatible Pass Gate

In this work, we propose a dual-port cell design to address the pass disturbance in vertical NAND storage, which can pass signals through a dedicated and string-compatible pass gate. We demonstrate that (i) the pass disturb-free feature originates from weakening of the depolarization field by the pass bias at the high-VTH (HVT) state and the screening of the applied field by the channel at the low-VTH (LVT) state; (ii) combined simulations and experimental demonstrations of dual-port design verify the disturb-free operation in a NAND string, overcoming a key challenge in single-port designs; (iii) the proposed design can be incorporated into a highly scaled vertical NAND FeFET string, and the pass gate can be incorporated into the existing three-dimensional (3D) NAND with the negligible overhead of the pass gate interconnection through a global bottom pass gate contact in the substrate.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

ACS Applied Materials & Interfaces

工程技术-材料科学:综合

CiteScore

16.00

自引率

6.30%

发文量

4978

审稿时长

1.8 months

期刊介绍:

ACS Applied Materials & Interfaces is a leading interdisciplinary journal that brings together chemists, engineers, physicists, and biologists to explore the development and utilization of newly-discovered materials and interfacial processes for specific applications. Our journal has experienced remarkable growth since its establishment in 2009, both in terms of the number of articles published and the impact of the research showcased. We are proud to foster a truly global community, with the majority of published articles originating from outside the United States, reflecting the rapid growth of applied research worldwide.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: