为三级单元 3D NAND 闪存设计超晶格铁电-金属场效应晶体管

IF 3.1

4区 工程技术

Q2 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

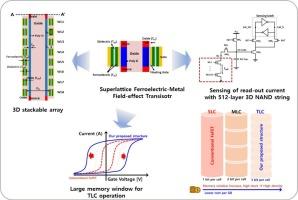

研究了基于超晶格铁电-金属场效应晶体管(SL-FeMFET)的三维 NAND 架构(3D NAND),用于三电平单元(TLC)操作。SL-FeMFET 展示了一种使用铁电/介电/铁电超晶格设计栅极堆栈的新方法,可实现 3D NAND 架构的大内存窗口 ∼ 3.48 V,程序/擦除电压为 ±7 V。通过 TCAD 建模,我们演示了 SL-FeMFET 的 TLC 运行,改善了存储器窗口,并减轻了 FeMFET 结构中浮动金属层引起的变化。此外,当垂直栅极堆叠从 256 层增加到 512 层时,我们使用页面缓冲电路对 TLC 检测的读出电流和 7 次读取操作中的最坏情况进行了研究。仿真结果表明,基于 SL-FeMFET 的 3D NAND 架构可以在 512 层上运行,并为 TLC 运行提供足够的感应裕量。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Design of Superlattice Ferroelectric-Metal Field-effect Transistor for triple-level cell 3D NAND flash

Superlattice ferroelectric-metal field-effect transistor (SL-FeMFET) based three-dimensional NAND architecture (3D NAND) is investigated for triple-level cell (TLC) operations. The SL-FeMFET shows a novel approach for designing the gate-stack using a superlattice of ferroelectric/dielectric/ferroelectric for achieving large memory window ∼3.48 V with program/erase voltage ±7 V for 3D NAND architecture. By TCAD modeling, we demonstrate TLC operation of SL-FeMFET with improving memory window and alleviating variability caused by floating metal layer in FeMFET structure. In addition, as the vertical gate stack increases from 256-layer to 512-layer, the read-out current with worst cases in seven read operations for TLC sensing are examined using page buffer circuit for sensing operation. The simulation results suggest that SL-FeMFET based 3D NAND architecture can operate 512-layer with sufficient sense margin for TLC operation.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Microelectronic Engineering

工程技术-工程:电子与电气

CiteScore

5.30

自引率

4.30%

发文量

131

审稿时长

29 days

期刊介绍:

Microelectronic Engineering is the premier nanoprocessing, and nanotechnology journal focusing on fabrication of electronic, photonic, bioelectronic, electromechanic and fluidic devices and systems, and their applications in the broad areas of electronics, photonics, energy, life sciences, and environment. It covers also the expanding interdisciplinary field of "more than Moore" and "beyond Moore" integrated nanoelectronics / photonics and micro-/nano-/bio-systems. Through its unique mixture of peer-reviewed articles, reviews, accelerated publications, short and Technical notes, and the latest research news on key developments, Microelectronic Engineering provides comprehensive coverage of this exciting, interdisciplinary and dynamic new field for researchers in academia and professionals in industry.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: