基于以交互为中心的存储和内存计算的可扩展通用伊辛机

IF 40.9

1区 工程技术

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

摘要

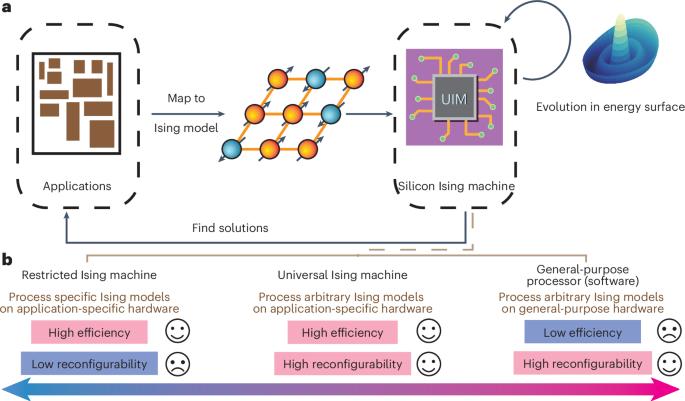

伊辛机是一种退火处理器,可以通过相应伊辛图的物理演化来解决组合优化问题。然而,由于自旋位置和连接是固定的,这类机器通常仅限于解决特定类型图拓扑的问题。在这里,我们报告了一种通用的伊辛机器,它能以合理的硬件资源支持任意伊辛图拓扑,使用粗粒度压缩稀疏行方法来压缩和存储稀疏伊辛图邻接矩阵。我们称这种以交互为中心的存储方法适用于任何类型的伊辛图,并能降低内存扩展成本。我们使用基于 40 纳米电阻式随机存取存储器阵列的内存计算硬件实验性地实现了 Ising 机器。与通用图形处理器相比,后者的速度提高了 442-1,450 倍,能耗降低了 4.1 × 105-6.0 × 105 倍。我们还利用伊辛机器解决了一个现实的电子设计自动化问题--多图案光刻布局分解,与典型中央处理器上的整数线性规划算法相比,速度提高了 390-65,550 倍。本文章由计算机程序翻译,如有差异,请以英文原文为准。

A scalable universal Ising machine based on interaction-centric storage and compute-in-memory

Ising machines are annealing processors that can solve combinatorial optimization problems via the physical evolution of the corresponding Ising graphs. Such machines are, however, typically restricted to solving problems with certain kinds of graph topology because the spin location and connections are fixed. Here, we report a universal Ising machine that supports arbitrary Ising graph topology with reasonable hardware resources using a coarse-grained compressed sparse row method to compress and store sparse Ising graph adjacency matrices. The approach, which we term interaction-centric storage, is suitable for any kind of Ising graph and reduces the memory scaling cost. We experimentally implement the Ising machine using compute-in-memory hardware based on a 40 nm resistive random-access memory arrays. We use the machine to solve max-cut and graph colouring problems, with the latter showing a 442–1,450 factor improvement in speed and 4.1 × 105–6.0 × 105 factor reduction in energy consumption compared to a general-purpose graphics processing unit. We also use our Ising machine to solve a realistic electronic design automation problem—multiple patterning lithography layout decomposition—with 390–65,550 times speedup compared to the integer linear programming algorithm on a typical central processing unit. An Ising machine that uses a coarse-grained compressed sparse row method to store sparse Ising graph adjacency matrices can be implemented with compute-in-memory hardware based on a resistive random-access memory array to efficiently solve combinatorial optimization problems.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

Nature Electronics

Engineering-Electrical and Electronic Engineering

CiteScore

47.50

自引率

2.30%

发文量

159

期刊介绍:

Nature Electronics is a comprehensive journal that publishes both fundamental and applied research in the field of electronics. It encompasses a wide range of topics, including the study of new phenomena and devices, the design and construction of electronic circuits, and the practical applications of electronics. In addition, the journal explores the commercial and industrial aspects of electronics research.

The primary focus of Nature Electronics is on the development of technology and its potential impact on society. The journal incorporates the contributions of scientists, engineers, and industry professionals, offering a platform for their research findings. Moreover, Nature Electronics provides insightful commentary, thorough reviews, and analysis of the key issues that shape the field, as well as the technologies that are reshaping society.

Like all journals within the prestigious Nature brand, Nature Electronics upholds the highest standards of quality. It maintains a dedicated team of professional editors and follows a fair and rigorous peer-review process. The journal also ensures impeccable copy-editing and production, enabling swift publication. Additionally, Nature Electronics prides itself on its editorial independence, ensuring unbiased and impartial reporting.

In summary, Nature Electronics is a leading journal that publishes cutting-edge research in electronics. With its multidisciplinary approach and commitment to excellence, the journal serves as a valuable resource for scientists, engineers, and industry professionals seeking to stay at the forefront of advancements in the field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: