基于铁电的 WS2 沟道场效应晶体管的逻辑内存应用,提高面积和能效

IF 8.8

2区 材料科学

Q1 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

摘要

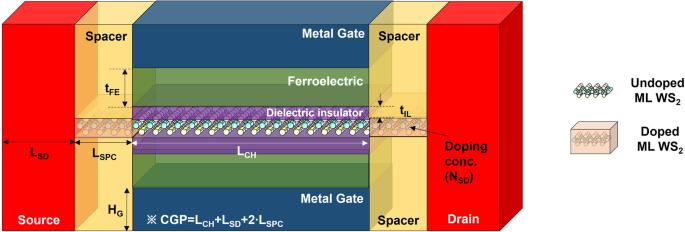

在本研究中,我们将铁电体应用于具有二维过渡金属二卤化物(TMDC)沟道的场效应晶体管(FET)的栅堆,积极研究 2 纳米以下技术节点的实现。随后,我们分析了内存逻辑(LiM)工作的电路特性,并在应用铁电后利用 LiM 特性实现了单器件配置。基于校准良好的模拟,我们在电路模拟器中进行了紧凑建模,以描述具有双栅极结构和二维沟道(DG 2D-FeFET)的铁电 FET 在亚 2 纳米尺寸下随温度变化的电气特性。通过这一研究,我们证实,与基于二维场效应晶体管的传统 CMOS 技术相比,为 2 纳米技术节点设计的基于二维铁电场效应晶体管的 LiM 技术在所有温度条件下的延迟、功率/能耗和电路面积方面都表现出更优越的特性。这一验证证明了二维场效应晶体管未来在极度缩小的技术节点中的技术潜力。本文章由计算机程序翻译,如有差异,请以英文原文为准。

Logic-in-memory application of ferroelectric-based WS2-channel field-effect transistors for improved area and energy efficiency

In this study, we applied ferroelectrics to the gate stack of Field Effect Transistors (FETs) with a 2D transition-metal dichalcogenide (TMDC) channel, actively researching for sub-2nm technology node implementation. Subsequently, we analyzed the circuit characteristics of Logic-in-Memory (LiM) operation and utilized LiM features after applying ferroelectrics to achieve a single-device configuration. Based on well-calibrated simulations, we performed compact modeling in a circuit simulator to depict the temperature-dependent electrical characteristics of ferroelectric FETs with a double gate structure and 2D channel (DG 2D-FeFET) in sub-2nm dimensions. Through this, we have confirmed that the 2D FeFET-based LiM technology, designed for the 2 nm technology node, exhibits superior characteristics in terms of delay, power/energy consumption, and circuit area under all temperature conditions, compared to the conventional CMOS technology based on 2D FETs. This verification serves as proof of the future technological potential of 2D-FeFET in extremely scaled-down technology nodes.

求助全文

通过发布文献求助,成功后即可免费获取论文全文。

去求助

来源期刊

npj 2D Materials and Applications

Engineering-Mechanics of Materials

CiteScore

14.50

自引率

2.10%

发文量

80

审稿时长

15 weeks

期刊介绍:

npj 2D Materials and Applications publishes papers on the fundamental behavior, synthesis, properties and applications of existing and emerging 2D materials. By selecting papers with the potential for impact, the journal aims to facilitate the transfer of the research of 2D materials into wide-ranging applications.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: