LFSR generation for high test coverage and low hardware overhead

IF 1.1

4区 计算机科学

Q4 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 5

Abstract

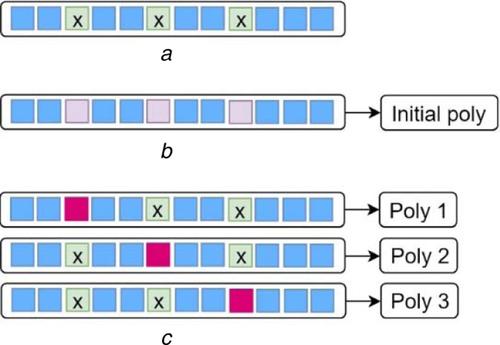

Safety-critical technology rests on optimised and effective testing techniques for every embedded system involved in the equipment. Pattern generator (PG) such as linear feedback shift register (LFSR) is used for fault detection and useful for reliability and online test. This study presents an analysis of the LFSR, using a known automatic test PG (ATPG) test set. Two techniques are undertaken to target difficult-to-detect faults with their respective trade-off analysis. This is achieved using Berlekamp-Massey (BM) algorithm with optimisations to reduce area overhead. The first technique (concatenated) combines all test sets generating a single polynomial that covers complete ATPG set (baseline-C). Improvements are found in Algorithm 1 reducing polynomial size through Xs assignment. The second technique uses non-concatenated test sets and provides a group of LFSRs using BM without including any optimisation (baseline-N). This algorithm is further optimised by selecting full mapping and independent polynomial expressions. Results are generated using 32 benchmarks and 65 nm technology. The concatenated technique provides reductions on area overhead for 90.6% cases with a best case of 57 and 39% means. The remaining 9.4% of cases, non-concatenated technique provides the best reduction of 37 with 1.4% means, whilst achieving 100% test mapping in both cases.

LFSR生成可实现高测试覆盖率和低硬件开销

安全关键技术依赖于设备中涉及的每个嵌入式系统的优化和有效的测试技术。模式发生器(PG),如线性反馈移位寄存器(LFSR),用于故障检测和可靠性在线测试。本研究使用已知的自动测试PG(ATPG)测试集对LFSR进行了分析。针对难以检测的故障,采用了两种技术,分别进行权衡分析。这是使用Berlekamp–Massey(BM)算法实现的,该算法经过优化以减少区域开销。第一种技术(级联)组合所有测试集,生成覆盖完整ATPG集(基线-C)的单个多项式。在算法1中发现了通过X赋值来减小多项式大小的改进。第二种技术使用非级联测试集,并使用BM提供一组LFSR,而不包括任何优化(基线-N)。该算法通过选择全映射和独立多项式表达式来进一步优化。使用32个基准和65nm技术生成结果。级联技术在90.6%的情况下减少了面积开销,最佳情况下平均值为57%和39%。在剩下的9.4%的病例中,非级联技术提供了最好的减少37例,平均值为1.4%,同时在两种情况下都实现了100%的测试映射。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

IET Computers and Digital Techniques

工程技术-计算机:理论方法

CiteScore

3.50

自引率

0.00%

发文量

12

审稿时长

>12 weeks

期刊介绍:

IET Computers & Digital Techniques publishes technical papers describing recent research and development work in all aspects of digital system-on-chip design and test of electronic and embedded systems, including the development of design automation tools (methodologies, algorithms and architectures). Papers based on the problems associated with the scaling down of CMOS technology are particularly welcome. It is aimed at researchers, engineers and educators in the fields of computer and digital systems design and test.

The key subject areas of interest are:

Design Methods and Tools: CAD/EDA tools, hardware description languages, high-level and architectural synthesis, hardware/software co-design, platform-based design, 3D stacking and circuit design, system on-chip architectures and IP cores, embedded systems, logic synthesis, low-power design and power optimisation.

Simulation, Test and Validation: electrical and timing simulation, simulation based verification, hardware/software co-simulation and validation, mixed-domain technology modelling and simulation, post-silicon validation, power analysis and estimation, interconnect modelling and signal integrity analysis, hardware trust and security, design-for-testability, embedded core testing, system-on-chip testing, on-line testing, automatic test generation and delay testing, low-power testing, reliability, fault modelling and fault tolerance.

Processor and System Architectures: many-core systems, general-purpose and application specific processors, computational arithmetic for DSP applications, arithmetic and logic units, cache memories, memory management, co-processors and accelerators, systems and networks on chip, embedded cores, platforms, multiprocessors, distributed systems, communication protocols and low-power issues.

Configurable Computing: embedded cores, FPGAs, rapid prototyping, adaptive computing, evolvable and statically and dynamically reconfigurable and reprogrammable systems, reconfigurable hardware.

Design for variability, power and aging: design methods for variability, power and aging aware design, memories, FPGAs, IP components, 3D stacking, energy harvesting.

Case Studies: emerging applications, applications in industrial designs, and design frameworks.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: