Power-efficient reliable register file for aggressive-environment applications

IF 1.1

4区 计算机科学

Q4 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 0

Abstract

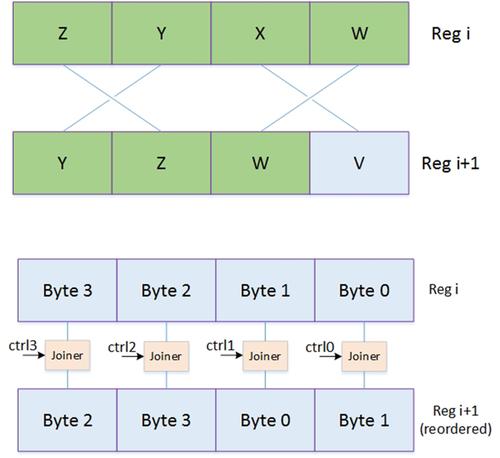

In a context of increasing demands for on-board data processing, insuring reliability under reduced power budget is a serious design challenge for embedded system manufacturers. Particularly, embedded processors in aggressive environments need to be designed with error hardening as a primary goal, not an afterthought. As Register File (RF) is a critical element within the processor pipeline, enhancing RF reliability is mandatory to design fault immune computing systems. This study proposes integer and floating point RF reliability enhancement techniques. Specifically, the authors propose Adjacent Register Hardened RF, a new RF architecture that exploits the adjacent byte-level narrow-width values for hardening integer registers at runtime. Registers are paired together by special switches referred to as joiners and non-utilised bits of each register are exploited to enhance the reliability of its counterpart register. Moreover, they suggest sacrificing the least significant bits of the Mantissa to enhance the reliability of the floating point critical bits, namely, Exponent and Sign bits. The authors’ results show that with a low power budget compared to state of the art techniques, they achieve better results under both normal and highly aggressive operating conditions.

高效可靠的寄存器文件,适用于攻击性环境应用

在对板载数据处理需求不断增加的背景下,在降低功率预算的情况下确保可靠性对嵌入式系统制造商来说是一个严峻的设计挑战。特别是,在攻击性环境中的嵌入式处理器需要将错误强化作为主要目标来设计,而不是事后考虑。由于寄存器文件(RF)是处理器流水线中的一个关键元素,因此增强RF可靠性对于设计故障免疫计算系统是强制性的。本研究提出了整数和浮点射频可靠性增强技术。具体而言,作者提出了相邻寄存器硬化RF,这是一种新的RF架构,它利用相邻字节级窄宽度值在运行时硬化整数寄存器。寄存器由称为连接器的特殊开关配对在一起,每个寄存器的未使用位被用来提高其对应寄存器的可靠性。此外,他们建议牺牲Mantissa的最低有效位来提高浮点关键位(即Exponent和Sign位)的可靠性。作者的研究结果表明,与现有技术相比,它们的功率预算较低,在正常和高度激进的操作条件下都能获得更好的结果。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

IET Computers and Digital Techniques

工程技术-计算机:理论方法

CiteScore

3.50

自引率

0.00%

发文量

12

审稿时长

>12 weeks

期刊介绍:

IET Computers & Digital Techniques publishes technical papers describing recent research and development work in all aspects of digital system-on-chip design and test of electronic and embedded systems, including the development of design automation tools (methodologies, algorithms and architectures). Papers based on the problems associated with the scaling down of CMOS technology are particularly welcome. It is aimed at researchers, engineers and educators in the fields of computer and digital systems design and test.

The key subject areas of interest are:

Design Methods and Tools: CAD/EDA tools, hardware description languages, high-level and architectural synthesis, hardware/software co-design, platform-based design, 3D stacking and circuit design, system on-chip architectures and IP cores, embedded systems, logic synthesis, low-power design and power optimisation.

Simulation, Test and Validation: electrical and timing simulation, simulation based verification, hardware/software co-simulation and validation, mixed-domain technology modelling and simulation, post-silicon validation, power analysis and estimation, interconnect modelling and signal integrity analysis, hardware trust and security, design-for-testability, embedded core testing, system-on-chip testing, on-line testing, automatic test generation and delay testing, low-power testing, reliability, fault modelling and fault tolerance.

Processor and System Architectures: many-core systems, general-purpose and application specific processors, computational arithmetic for DSP applications, arithmetic and logic units, cache memories, memory management, co-processors and accelerators, systems and networks on chip, embedded cores, platforms, multiprocessors, distributed systems, communication protocols and low-power issues.

Configurable Computing: embedded cores, FPGAs, rapid prototyping, adaptive computing, evolvable and statically and dynamically reconfigurable and reprogrammable systems, reconfigurable hardware.

Design for variability, power and aging: design methods for variability, power and aging aware design, memories, FPGAs, IP components, 3D stacking, energy harvesting.

Case Studies: emerging applications, applications in industrial designs, and design frameworks.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: