Mapping application-specific topology to mesh topology with reconfigurable switches

IF 1.1

4区 计算机科学

Q4 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 1

Abstract

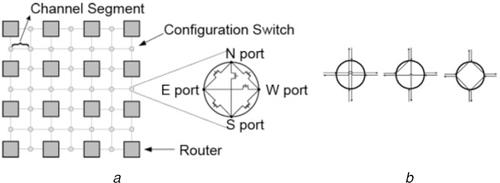

When designing a Network-on-Chip (NoC) architecture, designers must consider various criteria such as bandwidth, performance, energy consumption, cost, re-usability, and fault tolerance. In most of the design efforts, it is very difficult to meet all these interacting constraints and objectives at the same time. Some of these parameters can be optimised and met easily by regular NoC topologies due to their re-usability and fault-tolerance capabilities. On the other hand, other parameters such as energy consumption, performance, and chip area can be better optimised in irregular NoC topologies. In this work, the authors present a novel two-step method that combines the advantages of regular and irregular NoC topologies. In the first step, the authors' method generates an energy and area optimised irregular topology for the given application by using a genetic algorithm. The generated topology uses the least amount of routers and links to minimise the area and energy; thus, it offers only one routing path between communicating nodes. Therefore, it does not fault tolerant. In the second step, their method maps the generated irregular topology to a reconfigurable mesh topology to make it fault tolerant. The detailed simulation results show the superiority of the proposed method over the existing work on several multimedia benchmarks.

使用可重新配置的交换机将特定应用拓扑映射到网状拓扑

在设计片上网络(NoC)架构时,设计者必须考虑各种标准,如带宽、性能、能耗、成本、可重用性和容错性。在大多数设计工作中,很难同时满足所有这些相互作用的约束和目标。其中一些参数可以通过常规的NoC拓扑结构进行优化和满足,因为它们具有可重用性和容错能力。另一方面,在不规则的NoC拓扑中,可以更好地优化诸如能耗、性能和芯片面积之类的其他参数。在这项工作中,作者提出了一种新的两步方法,该方法结合了规则和不规则NoC拓扑的优点。在第一步中,作者的方法通过使用遗传算法为给定的应用生成能量和面积优化的不规则拓扑。生成的拓扑使用最少数量的路由器和链路来最小化面积和能量;因此,它在通信节点之间只提供一条路由路径。因此,它不是容错的。在第二步中,他们的方法将生成的不规则拓扑映射到可重新配置的网格拓扑,使其具有容错性。详细的仿真结果表明,该方法在几个多媒体基准上优于现有的工作。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

IET Computers and Digital Techniques

工程技术-计算机:理论方法

CiteScore

3.50

自引率

0.00%

发文量

12

审稿时长

>12 weeks

期刊介绍:

IET Computers & Digital Techniques publishes technical papers describing recent research and development work in all aspects of digital system-on-chip design and test of electronic and embedded systems, including the development of design automation tools (methodologies, algorithms and architectures). Papers based on the problems associated with the scaling down of CMOS technology are particularly welcome. It is aimed at researchers, engineers and educators in the fields of computer and digital systems design and test.

The key subject areas of interest are:

Design Methods and Tools: CAD/EDA tools, hardware description languages, high-level and architectural synthesis, hardware/software co-design, platform-based design, 3D stacking and circuit design, system on-chip architectures and IP cores, embedded systems, logic synthesis, low-power design and power optimisation.

Simulation, Test and Validation: electrical and timing simulation, simulation based verification, hardware/software co-simulation and validation, mixed-domain technology modelling and simulation, post-silicon validation, power analysis and estimation, interconnect modelling and signal integrity analysis, hardware trust and security, design-for-testability, embedded core testing, system-on-chip testing, on-line testing, automatic test generation and delay testing, low-power testing, reliability, fault modelling and fault tolerance.

Processor and System Architectures: many-core systems, general-purpose and application specific processors, computational arithmetic for DSP applications, arithmetic and logic units, cache memories, memory management, co-processors and accelerators, systems and networks on chip, embedded cores, platforms, multiprocessors, distributed systems, communication protocols and low-power issues.

Configurable Computing: embedded cores, FPGAs, rapid prototyping, adaptive computing, evolvable and statically and dynamically reconfigurable and reprogrammable systems, reconfigurable hardware.

Design for variability, power and aging: design methods for variability, power and aging aware design, memories, FPGAs, IP components, 3D stacking, energy harvesting.

Case Studies: emerging applications, applications in industrial designs, and design frameworks.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: