A 128 Gbps PAM-4 feed forward equaliser with optimized 1UI pulse generator in 65 nm CMOS

IF 1

4区 工程技术

Q4 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

Abstract

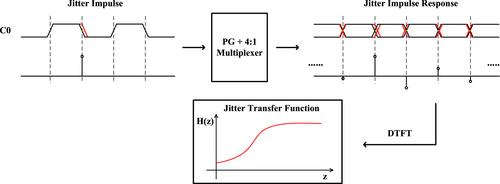

A quarter-rate PAM-4 FFE employing INCC 1UIPG is implemented in 65 nm CMOS. The proposed INNC 1UIPG reduces the average transition time by ~20%, saving clocking power consumption by ~1.5X, lowering jitter amplification by about 2~5 dB compared with previous works. Along with the bandwidth- and power-efficient partially segmented tailless 1-stage front-end architecture, the proposed FFE achieves 128Gbps PAM-4 data rate with a 0.014 mm2 area.

128 Gbps PAM-4前馈均衡器,采用65 nm CMOS优化的1UI脉冲发生器

采用INCC 1UIPG的四分之一速率PAM-4 FFE在65nm CMOS中实现。与以前的工作相比,所提出的INNC 1UIPG将平均转换时间减少了约20%,时钟功耗节省了约1.5X,抖动放大降低了约2~5dB。与带宽和功率高效的部分分段无尾1级前端架构一起,所提出的FFE实现了面积为0.014mm2的128Gbps PAM-4数据速率。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Iet Circuits Devices & Systems

工程技术-工程:电子与电气

CiteScore

3.80

自引率

7.70%

发文量

32

审稿时长

3 months

期刊介绍:

IET Circuits, Devices & Systems covers the following topics:

Circuit theory and design, circuit analysis and simulation, computer aided design

Filters (analogue and switched capacitor)

Circuit implementations, cells and architectures for integration including VLSI

Testability, fault tolerant design, minimisation of circuits and CAD for VLSI

Novel or improved electronic devices for both traditional and emerging technologies including nanoelectronics and MEMs

Device and process characterisation, device parameter extraction schemes

Mathematics of circuits and systems theory

Test and measurement techniques involving electronic circuits, circuits for industrial applications, sensors and transducers

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: