Ultra-compact neural network ADC exploiting ferroelectric FETs

IF 3.1

4区 工程技术

Q2 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

Abstract

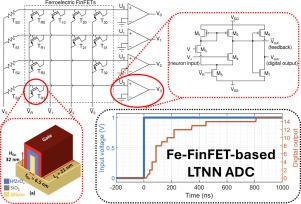

Development of ultra-compact, low-to-medium precision analog-to-digital converters (ADCs) with unprecedented energy-efficiency is essential to meet the ever-increasing demand for data converters in advanced computing systems including neuromorphic accelerators based on emerging non-volatile memories. To this end, in this work, for the first time, we propose a feedforward neural network ADC based on a network of highly scalable, CMOS-compatible, and energy efficient ferroelectric-FinFET (Fe-FinFET) synaptic elements. Our lower triangular neural network (LTNN) ADC design, implemented using 7-nm technology along with an experimentally calibrated compact model for Fe-FinFETs, consumes of power, 2.66 of area while operating at a speed of 1.23 megasamples per second for 4-bit precision. The proposed neural network ADC may pave the way for realization of highly efficient neuromorphic processing engines and neuro-optimizers based on cross-point array of emerging non-volatile memories.

利用铁电场效应管的超紧凑神经网络ADC

为了满足包括基于新兴非易失性存储器的神经形态加速器在内的先进计算系统对数据转换器日益增长的需求,开发具有前所未有能效的超紧凑、中低精度模数转换器(adc)至关重要。为此,在这项工作中,我们首次提出了一种前馈神经网络ADC,该网络基于高度可扩展,cmos兼容且节能的铁电- finfet (Fe-FinFET)突触元件网络。我们的下三角神经网络(LTNN) ADC设计采用7nm技术和实验校准的fe - finfet紧凑模型实现,功耗为5.44μW,面积为2.66 μm2,工作速度为1.23兆样本/秒,精度为4位。所提出的神经网络ADC可能为实现基于新兴非易失性存储器的交叉点阵列的高效神经形态处理引擎和神经优化器铺平道路。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Microelectronic Engineering

工程技术-工程:电子与电气

CiteScore

5.30

自引率

4.30%

发文量

131

审稿时长

29 days

期刊介绍:

Microelectronic Engineering is the premier nanoprocessing, and nanotechnology journal focusing on fabrication of electronic, photonic, bioelectronic, electromechanic and fluidic devices and systems, and their applications in the broad areas of electronics, photonics, energy, life sciences, and environment. It covers also the expanding interdisciplinary field of "more than Moore" and "beyond Moore" integrated nanoelectronics / photonics and micro-/nano-/bio-systems. Through its unique mixture of peer-reviewed articles, reviews, accelerated publications, short and Technical notes, and the latest research news on key developments, Microelectronic Engineering provides comprehensive coverage of this exciting, interdisciplinary and dynamic new field for researchers in academia and professionals in industry.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: