Thermal management materials for 3D-stacked integrated circuits

引用次数: 0

Abstract

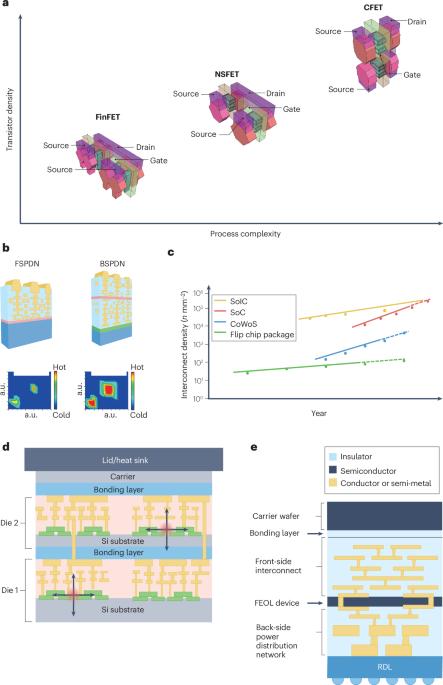

As transistor scaling approaches nanometre and even atomic scales, 3D stacking has become a critical enabler for advancement in the semiconductor industry, especially in high-performance computing and artificial intelligence (AI) applications. However, 3D integration introduces substantial thermal management challenges related to the increased power density and constrained heat dissipation pathways, particularly through low thermal conductivity interlayer dielectrics and complex interfaces. In this Review, we discuss state-of-the-art thermal management materials, covering their process compatibility, the critical integration challenges and the need for improved methods to enhance heat transport across interfaces. Advanced thermal characterization metrologies are introduced to highlight the need for non-destructive in-line metrologies. Finally, we provide a road map that outlines future research directions for material growth, integration and characterization methodologies to enable viable thermal solutions for 3D integration and beyond. The shrinking dimensions, the increased structural complexity and the 3D stacking of silicon-based semiconductor devices are intensifying challenges in thermal dissipation. This Review explores thermal management materials, integration challenges and characterization methods, and proposes a road map for efficient heat dissipation solutions in 3D integration.

用于3d堆叠集成电路的热管理材料

随着晶体管尺度接近纳米甚至原子尺度,3D堆叠已成为半导体行业进步的关键推动因素,特别是在高性能计算和人工智能(AI)应用中。然而,3D集成带来了大量的热管理挑战,涉及功率密度的增加和散热途径的限制,特别是通过低导热系数的层间电介质和复杂的界面。在这篇综述中,我们讨论了最先进的热管理材料,包括它们的工艺兼容性,关键的集成挑战以及改进方法来增强界面间的热传递的需求。介绍了先进的热表征计量,以突出非破坏性在线计量的需要。最后,我们提供了一个路线图,概述了材料生长,集成和表征方法的未来研究方向,以实现3D集成等可行的热解决方案。硅基半导体器件尺寸的不断缩小、结构复杂性的不断增加以及三维叠加都加剧了其在散热方面的挑战。本综述探讨了热管理材料、集成挑战和表征方法,并提出了3D集成中高效散热解决方案的路线图。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: