Ultra-low-power cryogenic complementary metal oxide semiconductor technology

引用次数: 0

Abstract

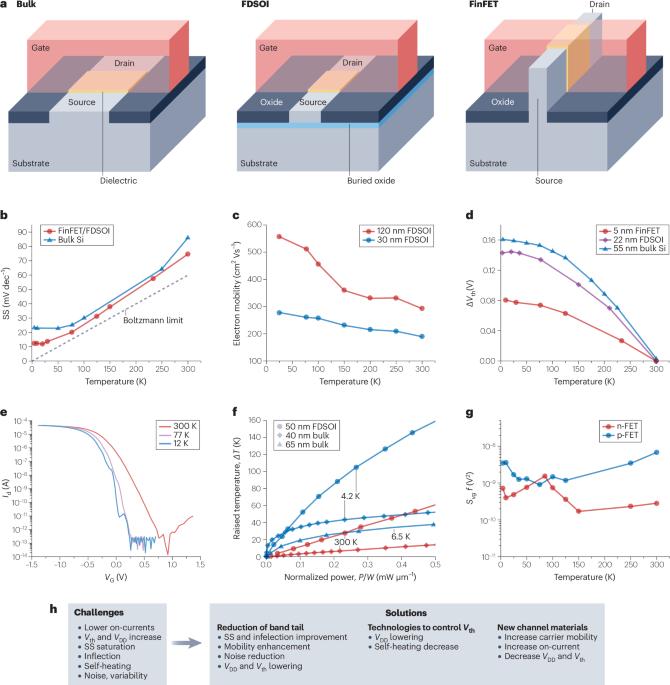

Universal cryogenic computing, encompassing von Neumann, neuromorphic and quantum computing, paves the way for future big-data processing with high energy efficiency. Complementary metal oxide semiconductor (CMOS) technology operating at cryogenic temperatures with ultra-low power consumption is a key component of this advancement. However, classical CMOS technology, designed for room temperature applications, suffers from band-tail effects at cryogenic levels, leading to an increased subthreshold swing and decreased mobility values. In addition, threshold voltages are enlarged. Thus, classical CMOS technology fails to meet the low power requirements when cooled close to zero Kelvin. In this Perspective, we show that steep slope cryogenic devices can be realized by screening the band tails with the use of high-k dielectrics and wrap-gate architectures and/or reducing them through the optimization of the surfaces and interfaces within the transistors. Cryogenic device functionality also strongly benefits from appropriate source/drain engineering employing dopant segregation from silicides. Furthermore, the threshold voltage control can be realized with back-gating, work-function engineering and dipole formation. As a major implication, future research and development towards cryogenic CMOS technology requires a combination of these approaches to enable universal cryogenic computing at the necessary ultra-low power levels. Ultra-low-power cryogenic complementary metal oxide semiconductor (cCMOS) technology is crucial for quantum computers. This Perspective highlights the challenges of the state-of-the-art technology and proposes solutions to mitigate band-tail effects, control the threshold voltage and achieve ultra-low-power cCMOS devices.

超低功耗低温互补金属氧化物半导体技术

通用低温计算,包括冯·诺伊曼、神经形态和量子计算,为未来高能效的大数据处理铺平了道路。在低温和超低功耗下工作的互补金属氧化物半导体(CMOS)技术是这一进步的关键组成部分。然而,为室温应用而设计的经典CMOS技术在低温水平下受到带尾效应的影响,导致亚阈值摆动增加和迁移率值降低。此外,阈值电压被放大。因此,当冷却到接近零开尔文时,传统的CMOS技术无法满足低功耗要求。在这个角度上,我们表明陡坡低温器件可以通过使用高k介电体和包栅结构来筛选带尾和/或通过优化晶体管内的表面和接口来减少它们来实现。低温装置的功能也强烈受益于适当的源/漏工程,采用从硅化物中分离掺杂剂。此外,阈值电压控制可以通过反门控、功函数工程和偶极子形成来实现。作为一个主要的影响,未来对低温CMOS技术的研究和发展需要这些方法的结合,以实现在必要的超低功耗水平下的通用低温计算。超低功耗低温互补金属氧化物半导体(cCMOS)技术是量子计算机的关键技术。本展望强调了最先进技术的挑战,并提出了缓解带尾效应、控制阈值电压和实现超低功耗cCMOS器件的解决方案。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: