A 5.56 ppm/°C curvature-compensated CMOS voltage reference using reverse body biasing technique

IF 3.2

3区 计算机科学

Q2 ENGINEERING, ELECTRICAL & ELECTRONIC

Aeu-International Journal of Electronics and Communications

Pub Date : 2025-09-11

DOI:10.1016/j.aeue.2025.155995

引用次数: 0

Abstract

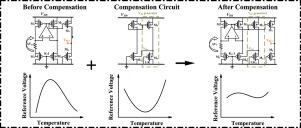

This paper presents a novel CMOS voltage reference featuring a low temperature coefficient (TC) and low power consumption. Based on the traditional low-voltage ZTC voltage reference architecture, a reverse body biasing temperature compensation technique is introduced into the loop. This approach significantly improves the performance of TC while reducing power consumption. The proposed voltage reference is designed and simulated using a CMOS process. Simulation results confirm that the reference voltage output is 678 mV, with an average temperature coefficient of 5.56 ppm/ over a temperature range of −40 °C to 100 °C. The PSRR of the proposed voltage reference is 64.82 dB at 100 Hz. It operates with a minimum supply voltage of 1.05 V, and the compensation circuit structure ensures minimal current consumption, leading to a power consumption of only 1.90 W, with a silicon area of 0.025 mm.

5.56 ppm/°C曲率补偿CMOS电压基准使用反向体偏置技术

本文提出了一种具有低温度系数和低功耗的新型CMOS电压基准。在传统低压ZTC电压基准结构的基础上,引入了逆体偏置温度补偿技术。这种方法在降低功耗的同时显著提高了TC的性能。采用0.18μm CMOS工艺设计并仿真了所提出的基准电压。仿真结果证实,参考电压输出为678 mV,平均温度系数为5.56 ppm/°C,温度范围为- 40°C至100°C。所提出的参考电压在100 Hz时的PSRR为64.82 dB。它的工作电压最低为1.05 V,补偿电路结构确保了最小的电流消耗,功耗仅为1.90 μW,硅面积为0.025 mm2。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

CiteScore

6.90

自引率

18.80%

发文量

292

审稿时长

4.9 months

期刊介绍:

AEÜ is an international scientific journal which publishes both original works and invited tutorials. The journal''s scope covers all aspects of theory and design of circuits, systems and devices for electronics, signal processing, and communication, including:

signal and system theory, digital signal processing

network theory and circuit design

information theory, communication theory and techniques, modulation, source and channel coding

switching theory and techniques, communication protocols

optical communications

microwave theory and techniques, radar, sonar

antennas, wave propagation

AEÜ publishes full papers and letters with very short turn around time but a high standard review process. Review cycles are typically finished within twelve weeks by application of modern electronic communication facilities.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: