A bit-level loosely coupled computing-in-memory macro with early termination

IF 1.9

3区 工程技术

Q3 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

Abstract

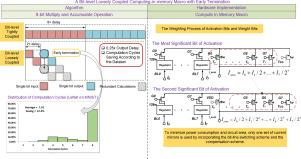

Computing-in-memory (CIM) has emerged as a promising solution for artificial intelligence (AI) edge devices. However, conventional bit-slicing CIM designs necessitate the availability of all input bits prior to the computation process. This tight coupling between input and output bits results in a substantial need for temporary storage and leads to significant output delays. In this article, we propose a bit-level loosely coupled (BLC) computation scheme for CIM macros, which reduces the bit widths of temporary data to 1 bit, thereby saving register demand. Accuracy and computational efficiency is further enhanced by zero detection scheme and early termination scheme. A CIM macro is designed to implement BLC multiply and accumulate (MAC) computation. Compared with the 8-bit quantized model, our proposed scheme incurs only 0.29% and 0.52% accuracy loss on AlexNet and ResNet20 (CIFAR-10 dataset), respectively. In a 40-nm process, the power consumption of our CIM macro is 3.54 mW (256 x 256 at 8-bit) and the computing-power ratio is 37.01 TOPS/W.

具有提前终止的位级松散耦合内存计算宏

内存计算(CIM)已成为人工智能(AI)边缘设备的一种有前途的解决方案。然而,传统的位切片CIM设计要求在计算过程之前所有输入位都可用。输入和输出位之间的这种紧密耦合导致对临时存储的大量需求,并导致显著的输出延迟。在本文中,我们提出了一种用于CIM宏的位级松耦合(BLC)计算方案,该方案将临时数据的位宽度减小到1位,从而节省了寄存器需求。零检测方案和早期终止方案进一步提高了精度和计算效率。设计了CIM宏来实现BLC的乘法累加(MAC)计算。与8位量化模型相比,我们提出的方案在AlexNet和ResNet20 (CIFAR-10数据集)上的准确率损失分别为0.29%和0.52%。在40纳米制程中,我们的CIM宏的功耗为3.54 mW(8位256 × 256),计算功率比为37.01 TOPS/W。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Microelectronics Journal

工程技术-工程:电子与电气

CiteScore

4.00

自引率

27.30%

发文量

222

审稿时长

43 days

期刊介绍:

Published since 1969, the Microelectronics Journal is an international forum for the dissemination of research and applications of microelectronic systems, circuits, and emerging technologies. Papers published in the Microelectronics Journal have undergone peer review to ensure originality, relevance, and timeliness. The journal thus provides a worldwide, regular, and comprehensive update on microelectronic circuits and systems.

The Microelectronics Journal invites papers describing significant research and applications in all of the areas listed below. Comprehensive review/survey papers covering recent developments will also be considered. The Microelectronics Journal covers circuits and systems. This topic includes but is not limited to: Analog, digital, mixed, and RF circuits and related design methodologies; Logic, architectural, and system level synthesis; Testing, design for testability, built-in self-test; Area, power, and thermal analysis and design; Mixed-domain simulation and design; Embedded systems; Non-von Neumann computing and related technologies and circuits; Design and test of high complexity systems integration; SoC, NoC, SIP, and NIP design and test; 3-D integration design and analysis; Emerging device technologies and circuits, such as FinFETs, SETs, spintronics, SFQ, MTJ, etc.

Application aspects such as signal and image processing including circuits for cryptography, sensors, and actuators including sensor networks, reliability and quality issues, and economic models are also welcome.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: