Reconfigurable Electro-Optic FET Based on Ferroelectric Electrostatic Doping toward Optical Field Programmable Gate Arrays

IF 6.7

1区 物理与天体物理

Q1 MATERIALS SCIENCE, MULTIDISCIPLINARY

引用次数: 0

Abstract

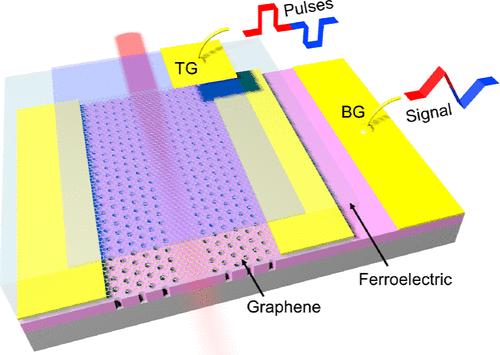

Silicon photonic integrated circuits have been extremely well developed and have gradually moved toward large-scale production. However, the limitations of current scaling have forced researchers to explore new avenues to achieve more compact integration and to develop more cost-effective silicon photonics components. Silicon photonic FPGAs are more area-efficient and flexible compared to traditional on-chip optical circuits due to their reconfigurable nature, which allows for the optimization of silicon photonic devices after fabrication. This feature enables a wide range of applications and performance requirements to be met with a single chip design, thereby reducing costs and enabling the rapid prototyping of new photonic circuits. Here, leveraging ferroelectric-doped graphene into a silicon field programmable gate array, we propose a compact reconfigurable electro-optical device with superior nonvolatility and reconfigurability, broadening the range of applications for programmable silicon photonics. Nonvolatile multilevel memory with electrical write and optical readout is implemented. This innovative memory system supports 10 distinct levels of electro-optical storage, providing enhanced capacity and flexibility. Carrier-enhanced and -depleted modes can be reconfigured by electrical programming on the same optical logic gate. Reconfigurable logic computing in the electronic and optical domain that takes advantage of this feature is demonstrated. Our work provides a compact new approach for programmable electro-optic field programmable gate arrays with low power consumption.

基于铁电静电掺杂的可重构光电场效应晶体管,面向光场可编程门阵列

硅光子集成电路已经发展得非常成熟,并逐步走向大规模生产。然而,由于目前规模的限制,研究人员不得不探索新的途径,以实现更紧凑的集成,并开发出更具成本效益的硅光子元件。硅光子 FPGA 与传统的片上光路相比,具有更高的面积效率和灵活性,这得益于其可重新配置的特性,即硅光子器件可以在制造后进行优化。这一特性使得单芯片设计能够满足广泛的应用和性能要求,从而降低成本,实现新光子电路的快速原型开发。在这里,我们利用掺铁石墨烯到硅现场可编程门阵列中,提出了一种紧凑型可重新配置的电子光学器件,它具有卓越的非挥发性和可重新配置性,拓宽了可编程硅光子学的应用范围。我们实现了具有电写入和光读出功能的非易失性多级存储器。这种创新的存储器系统支持 10 个不同级别的电光存储,提供了更大的容量和灵活性。载流子增强模式和载流子耗尽模式可通过同一光学逻辑门上的电子编程进行重新配置。我们展示了利用这一特点在电子和光学领域进行的可重构逻辑计算。我们的工作为低功耗可编程电光场可编程门阵列提供了一种紧凑的新方法。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

ACS Photonics

NANOSCIENCE & NANOTECHNOLOGY-MATERIALS SCIENCE, MULTIDISCIPLINARY

CiteScore

11.90

自引率

5.70%

发文量

438

审稿时长

2.3 months

期刊介绍:

Published as soon as accepted and summarized in monthly issues, ACS Photonics will publish Research Articles, Letters, Perspectives, and Reviews, to encompass the full scope of published research in this field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: