CMOS-compatible strain engineering for monolayer semiconductor transistors

IF 40.9

1区 工程技术

Q1 ENGINEERING, ELECTRICAL & ELECTRONIC

引用次数: 0

Abstract

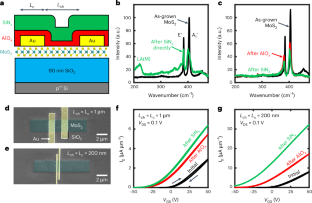

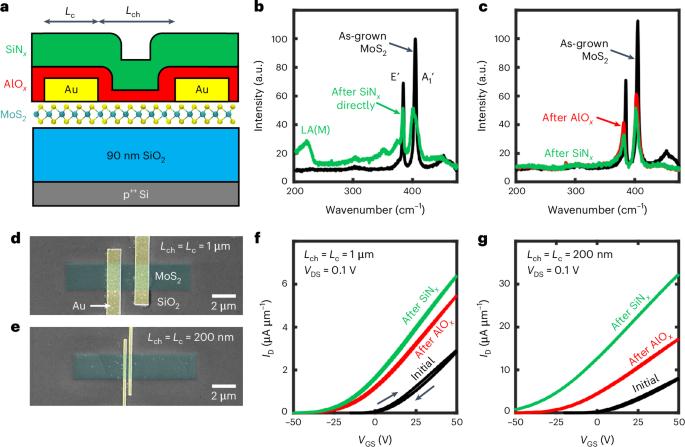

Strain engineering has played a key role in modern silicon electronics, having been introduced as a mobility booster in the 1990s and commercialized in the early 2000s. Achieving similar advances with two-dimensional (2D) semiconductors in a complementary metal–oxide–semiconductor (CMOS)-compatible manner could improve the industrial viability of 2D material transistors. Here, we show that silicon nitride capping layers can impart strain to monolayer molybdenum disulfide (MoS2) transistors on conventional silicon substrates, improving their performance with a CMOS-compatible approach, at a low thermal budget of 350 °C. Strained back-gated and dual-gated MoS2 transistors exhibit median increases in on-state current of up to 60% and 45%, respectively. The greatest improvements are found when reducing both transistor channels and contacts from micrometre-scale to 200 nm, reaching saturation currents of 488 µA µm−1 in devices with just 400 nm contact pitch. Simulations show that the performance enhancement is mainly due to tensile strain lowering the contact Schottky barriers, and that further reducing device dimensions, including contacts, could lead to additional increases in strain and performance. The on-current performance of MoS2-based transistors can be improved by using silicon nitride capping layers that apply strain to the devices.

单层半导体晶体管的 CMOS 兼容应变工程

应变工程在现代硅电子学中发挥了关键作用,它在 20 世纪 90 年代被引入作为移动性的助推器,并在 21 世纪初实现了商业化。以与互补金属氧化物半导体(CMOS)兼容的方式实现二维(2D)半导体的类似进步,可以提高二维材料晶体管的工业可行性。在这里,我们展示了氮化硅封盖层可以在传统硅衬底上向单层二硫化钼(MoS2)晶体管传递应变,从而在 350 ℃ 的低热预算条件下,通过 CMOS 兼容方法提高晶体管的性能。受约束背栅和双栅 MoS2 晶体管的导通电流中值分别增加了 60% 和 45%。当晶体管沟道和触点从微米级缩小到 200 纳米时,性能提升最大,在触点间距仅为 400 纳米的器件中,饱和电流达到 488 µA µm-1。模拟结果表明,性能的提高主要是由于拉伸应变降低了触点肖特基势垒,而进一步缩小器件尺寸(包括触点)可能会导致应变和性能的进一步提高。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Nature Electronics

Engineering-Electrical and Electronic Engineering

CiteScore

47.50

自引率

2.30%

发文量

159

期刊介绍:

Nature Electronics is a comprehensive journal that publishes both fundamental and applied research in the field of electronics. It encompasses a wide range of topics, including the study of new phenomena and devices, the design and construction of electronic circuits, and the practical applications of electronics. In addition, the journal explores the commercial and industrial aspects of electronics research.

The primary focus of Nature Electronics is on the development of technology and its potential impact on society. The journal incorporates the contributions of scientists, engineers, and industry professionals, offering a platform for their research findings. Moreover, Nature Electronics provides insightful commentary, thorough reviews, and analysis of the key issues that shape the field, as well as the technologies that are reshaping society.

Like all journals within the prestigious Nature brand, Nature Electronics upholds the highest standards of quality. It maintains a dedicated team of professional editors and follows a fair and rigorous peer-review process. The journal also ensures impeccable copy-editing and production, enabling swift publication. Additionally, Nature Electronics prides itself on its editorial independence, ensuring unbiased and impartial reporting.

In summary, Nature Electronics is a leading journal that publishes cutting-edge research in electronics. With its multidisciplinary approach and commitment to excellence, the journal serves as a valuable resource for scientists, engineers, and industry professionals seeking to stay at the forefront of advancements in the field.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: