A 15.13 mW 3.2 GHz 8-bit carry look-ahead adder using single-phase all-N-transistor logic

IF 2.2

3区 工程技术

Q3 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 0

Abstract

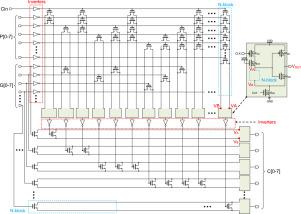

Adders are critical to the efficiency of arithmetic circuits in battery-powered electronic devices. This study demonstrates an 8-bit CLA (carry look-ahead adder) using single-phase ANT logic to increase the computation speed and reduce the power dissipation simultaneously. The single-phase ANT has no internal loop that optimizes the efficiency of the prior ANT. Utilizing a TSMC 40-nm technology, the proposed 8-bit CLA is fabricated. It attains the highest operating frequency of 3.2 GHz and the lowest normalized PDP (power delay product) by on-silicon measurement for 20 pF load.

使用单相全 N 晶体管逻辑的 15.13 mW 3.2 GHz 8 位进位前瞻加法器

加法器对电池供电电子设备中算术电路的效率至关重要。本研究展示了一种使用单相 ANT 逻辑的 8 位 CLA(进位前瞻加法器),可同时提高计算速度和降低功耗。单相 ANT 没有内部环路,从而优化了先前 ANT 的效率。利用台积电 40 纳米技术,制造出了拟议的 8 位 CLA。在 20 pF 负载条件下,通过硅上测量,它达到了 3.2 GHz 的最高工作频率和最低归一化 PDP(功率延迟积)。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Integration-The Vlsi Journal

工程技术-工程:电子与电气

CiteScore

3.80

自引率

5.30%

发文量

107

审稿时长

6 months

期刊介绍:

Integration''s aim is to cover every aspect of the VLSI area, with an emphasis on cross-fertilization between various fields of science, and the design, verification, test and applications of integrated circuits and systems, as well as closely related topics in process and device technologies. Individual issues will feature peer-reviewed tutorials and articles as well as reviews of recent publications. The intended coverage of the journal can be assessed by examining the following (non-exclusive) list of topics:

Specification methods and languages; Analog/Digital Integrated Circuits and Systems; VLSI architectures; Algorithms, methods and tools for modeling, simulation, synthesis and verification of integrated circuits and systems of any complexity; Embedded systems; High-level synthesis for VLSI systems; Logic synthesis and finite automata; Testing, design-for-test and test generation algorithms; Physical design; Formal verification; Algorithms implemented in VLSI systems; Systems engineering; Heterogeneous systems.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: