Neural architecture search for in-memory computing-based deep learning accelerators

引用次数: 0

Abstract

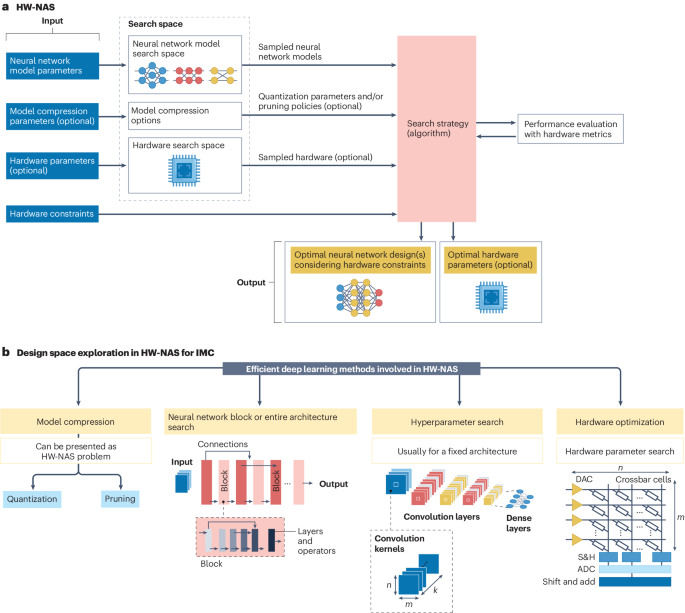

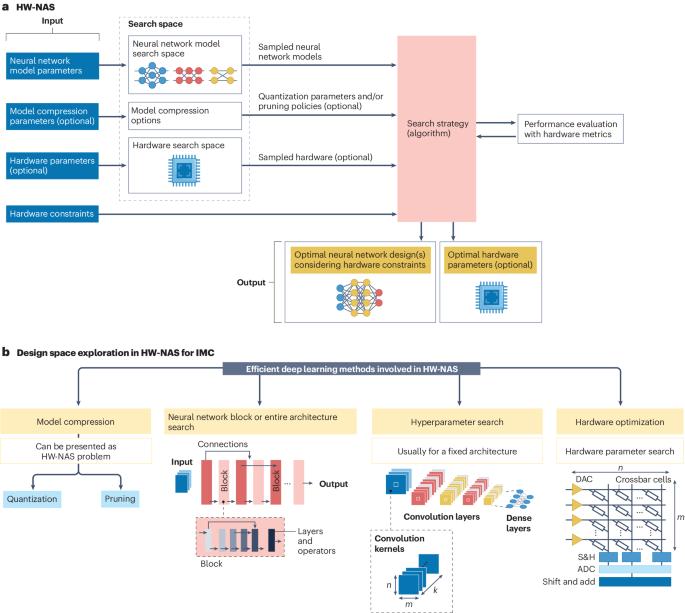

The rapid growth of artificial intelligence and the increasing complexity of neural network models are driving demand for efficient hardware architectures that can address power-constrained and resource-constrained deployments. In this context, the emergence of in-memory computing (IMC) stands out as a promising technology. For this purpose, several IMC devices, circuits and architectures have been developed. However, the intricate nature of designing, implementing and deploying such architectures necessitates a well-orchestrated toolchain for hardware–software co-design. This toolchain must allow IMC-aware optimizations across the entire stack, encompassing devices, circuits, chips, compilers, software and neural network design. The complexity and sheer size of the design space involved renders manual optimizations impractical. To mitigate these challenges, hardware-aware neural architecture search (HW-NAS) has emerged as a promising approach to accelerate the design of streamlined neural networks tailored for efficient deployment on IMC hardware. This Review illustrates the application of HW-NAS to the specific features of IMC hardware and compares existing optimization frameworks. Ongoing research and unresolved issues are discussed. A roadmap for the evolution of HW-NAS for IMC architectures is proposed. Hardware-aware neural architecture search (HW-NAS) can be used to design efficient in-memory computing (IMC) hardware for deep learning accelerators. This Review discusses methodologies, frameworks, ongoing research, open issues and recommendations, and provides a roadmap for HW-NAS for IMC.

基于内存计算的深度学习加速器的神经架构搜索

人工智能的快速发展和神经网络模型复杂性的不断提高,推动了对高效硬件架构的需求,这种架构可以解决功耗和资源受限的部署问题。在此背景下,内存计算(IMC)作为一种前景广阔的技术脱颖而出。为此,人们开发了多种 IMC 设备、电路和架构。然而,由于设计、实施和部署此类架构的复杂性,有必要为硬件-软件协同设计提供一个精心设计的工具链。该工具链必须允许在整个堆栈中进行 IMC 感知优化,包括器件、电路、芯片、编译器、软件和神经网络设计。设计空间的复杂性和规模使得手动优化变得不切实际。为缓解这些挑战,硬件感知神经架构搜索(HW-NAS)已成为一种很有前途的方法,可加速设计精简的神经网络,以便在 IMC 硬件上高效部署。本综述说明了 HW-NAS 在 IMC 硬件特定功能上的应用,并对现有优化框架进行了比较。文中还讨论了正在进行的研究和尚未解决的问题。本文提出了针对 IMC 架构的 HW-NAS 发展路线图。硬件感知神经架构搜索(HW-NAS)可用于为深度学习加速器设计高效的内存计算(IMC)硬件。本综述讨论了方法论、框架、正在进行的研究、开放性问题和建议,并提供了用于 IMC 的 HW-NAS 路线图。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: