Memristor-based hardware accelerators for artificial intelligence

引用次数: 0

Abstract

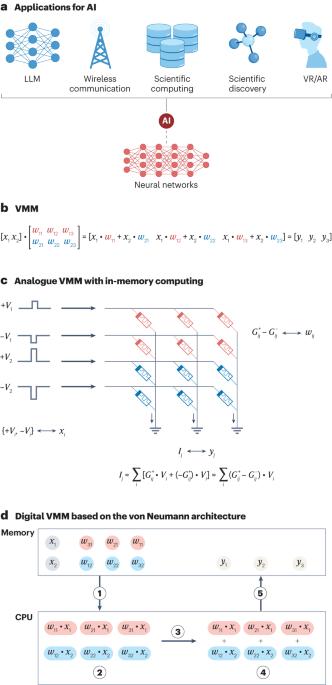

Satisfying the rapid evolution of artificial intelligence (AI) algorithms requires exponential growth in computing resources, which, in turn, presents huge challenges for deploying AI models on hardware. Memristor-based hardware accelerators provide a promising solution to the energy efficiency and latency issues in large AI model deployments. The non-volatility of memristive devices facilitates in-memory computing, in which computing occurs within memory cells where data are stored. This approach eliminates the constant data shuttling between the processing and memory units found in the von Neumann architecture, resulting in substantial time and energy savings. The recent surge of research and development in this field indicates a pivotal transition of memristor technology from proof-of-concept demonstrations to commercial products that accelerate AI models across various applications. In this Review, we survey the latest progress in memristive crossbar arrays, peripheral circuits, architectures, hardware–software co-designs and system implementations for memristor-based hardware accelerators. We discuss how these research efforts bridge the gap between memristive devices and energy-efficient accelerators for AI. Finally, we summarize the key remaining issues and propose potential pathways to future hardware accelerators with low latency and high energy efficiency, emphasizing the technology scale-up and commercialization for large-scale AI applications. This Review summarizes latest advancements in memristor-based hardware accelerators, an energy-efficient solution for computing-intensive artificial intelligence algorithms, covering crossbar arrays, peripheral circuits, architectures and software–hardware co-designs. It analyses challenges and pathways for the transition of memristor technology to commercial products.

基于 Memristor 的人工智能硬件加速器

满足人工智能(AI)算法的快速发展需要计算资源的指数级增长,这反过来又给在硬件上部署人工智能模型带来了巨大挑战。基于 Memristor 的硬件加速器为解决大型人工智能模型部署中的能效和延迟问题提供了一种前景广阔的解决方案。Memristive 器件的非挥发性有利于内存计算,即在存储数据的内存单元内进行计算。这种方法消除了冯-诺依曼架构中处理单元和内存单元之间的持续数据穿梭,从而节省了大量时间和能源。最近,这一领域的研究和开发热潮表明,忆阻器技术正在从概念验证演示向商业产品过渡,从而加速各种应用中的人工智能模型。在这篇综述中,我们将探讨基于忆阻器的硬件加速器在忆阻器横杆阵列、外围电路、架构、软硬件协同设计和系统实现方面的最新进展。我们将讨论这些研究工作如何在人工智能的忆阻器件和高能效加速器之间架起一座桥梁。最后,我们总结了余下的关键问题,并提出了未来实现低延迟、高能效硬件加速器的潜在途径,同时强调了针对大规模人工智能应用的技术扩展和商业化。本综述总结了基于忆阻器的硬件加速器的最新进展,这是一种针对计算密集型人工智能算法的高能效解决方案,涵盖了交叉条阵列、外围电路、架构和软硬件协同设计。报告分析了将忆阻器技术转化为商业产品所面临的挑战和途径。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: