Isla: integrating full-scale ISA semantics and axiomatic concurrency models (extended version)

IF 0.8

4区 计算机科学

Q3 COMPUTER SCIENCE, THEORY & METHODS

引用次数: 0

Abstract

Abstract Architecture specifications such as Armv8-A and RISC-V are the ultimate foundation for software verification and the correctness criteria for hardware verification. They should define the allowed sequential and relaxed-memory concurrency behaviour of programs, but hitherto there has been no integration of full-scale instruction-set architecture (ISA) semantics with axiomatic concurrency models, either in mathematics or in tools. These ISA semantics can be surprisingly large and intricate, e.g. 100k $$+$$

Isla:集成全面ISA语义和公理并发模型(扩展版本)

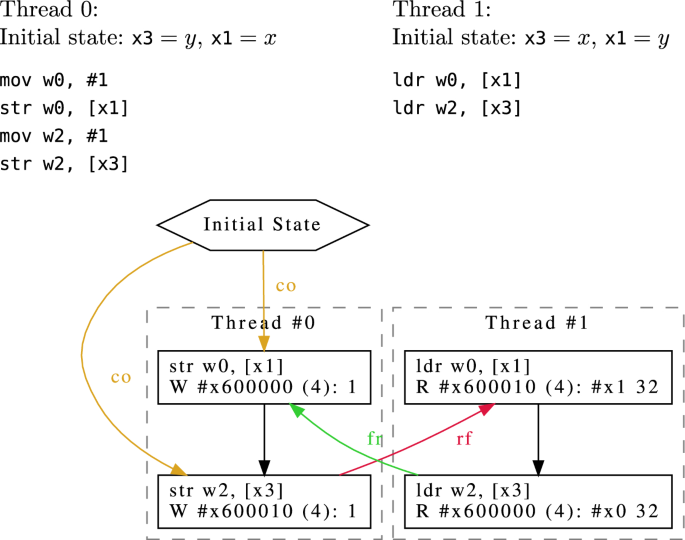

Armv8-A和RISC-V等体系结构规范是软件验证的最终基础,也是硬件验证的正确性标准。它们应该定义程序允许的顺序和松弛内存并发行为,但迄今为止,无论是在数学还是在工具中,还没有将全面指令集架构(ISA)语义与公理并发模型集成起来。这些ISA语义可能非常庞大和复杂,例如Armv8-A的100,000行$$+$$ +行。在本文中,我们提出了一个工具Isla,用于计算与Sail语言中全面ISA定义和Cat语言中任意公理松弛内存并发模型相关的并发石蕊测试的允许行为。它基于Sail ISA规范的通用符号引擎。我们为该工具配备了一个web界面,使其易于访问,并在Armv8-A和RISC-V上对其进行了说明和评估。符号执行引擎对于其他验证任务也很有价值:它已用于Arm Morello原型架构的自动化ISA测试生成,扩展了具有CHERI功能的Armv8-A,以及用于Armv8-A和RISC-V ISA规范之上的二进制代码的Iris程序逻辑推理。通过使用全面和权威的ISA语义,Isla允许使用任意用户指令以高置信度评估石蕊测试。此外,由于这些ISA规范给出了管理程序和操作系统所使用的系统功能的顺序方面的详细且经过验证的定义,例如指令获取、异常和地址转换,因此我们的工具为开发这些方面的并发语义提供了基础。我们为Armv8-A指令获取和虚拟内存模型以及Simner等人的示例演示了这一点。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Formal Methods in System Design

工程技术-计算机:理论方法

CiteScore

2.00

自引率

12.50%

发文量

16

审稿时长

>12 weeks

期刊介绍:

The focus of this journal is on formal methods for designing, implementing, and validating the correctness of hardware (VLSI) and software systems. The stimulus for starting a journal with this goal came from both academia and industry. In both areas, interest in the use of formal methods has increased rapidly during the past few years. The enormous cost and time required to validate new designs has led to the realization that more powerful techniques must be developed. A number of techniques and tools are currently being devised for improving the reliability, and robustness of complex hardware and software systems. While the boundary between the (sub)components of a system that are cast in hardware, firmware, or software continues to blur, the relevant design disciplines and formal methods are maturing rapidly. Consequently, an important (and useful) collection of commonly applicable formal methods are expected to emerge that will strongly influence future design environments and design methods.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: