Concise outlines for a complex logic: a proof outline checker for TaDA

IF 0.8

4区 计算机科学

Q3 COMPUTER SCIENCE, THEORY & METHODS

引用次数: 6

Abstract

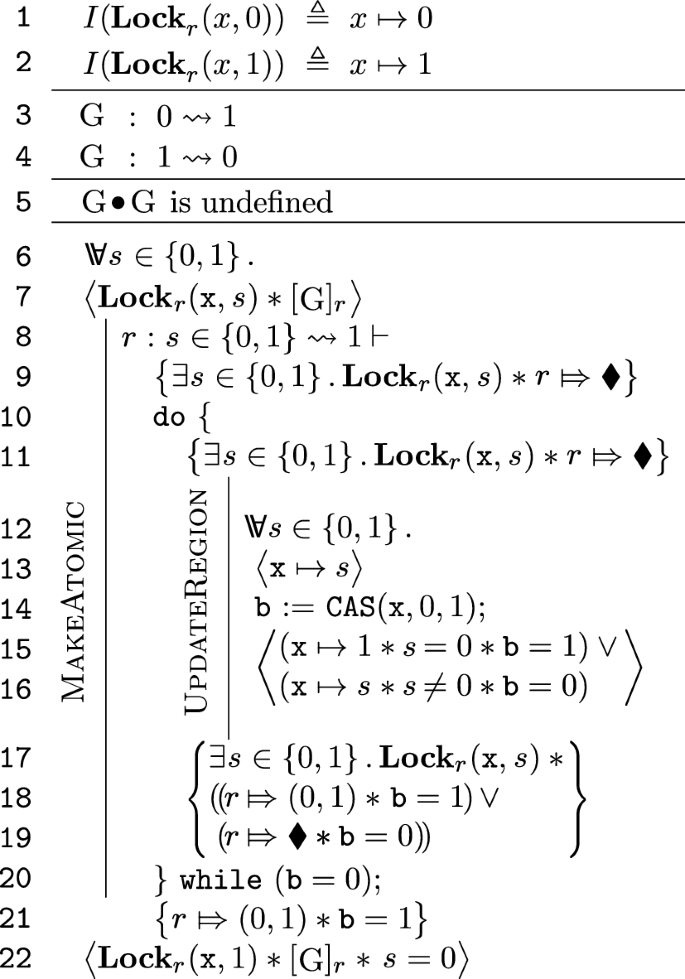

Abstract Modern separation logics allow one to prove rich properties of intricate code, e.g., functional correctness and linearizability of non-blocking concurrent code. However, this expressiveness leads to a complexity that makes these logics difficult to apply. Manual proofs or proofs in interactive theorem provers consist of a large number of steps, often with subtle side conditions. On the other hand, automation with dedicated verifiers typically requires sophisticated proof search algorithms that are specific to the given program logic, resulting in limited tool support that makes it difficult to experiment with program logics, e.g., when learning, improving, or comparing them. Proof outline checkers fill this gap. Their input is a program annotated with the most essential proof steps, just like the proof outlines typically presented in papers. The tool then checks automatically that this outline represents a valid proof in the program logic. In this paper, we systematically develop a proof outline checker for the TaDA logic, which reduces the checking to a simpler verification problem, for which automated tools exist. Our approach leads to proof outline checkers that provide substantially more automation than interactive provers, but are much simpler to develop than custom automatic verifiers.

复杂逻辑的简明大纲:TaDA的证明大纲检查器

现代分离逻辑允许人们证明复杂代码的丰富属性,例如,非阻塞并发代码的功能正确性和线性性。然而,这种表达性导致了复杂性,使得这些逻辑难以应用。手工证明或交互式定理证明中的证明由大量步骤组成,通常带有微妙的边条件。另一方面,具有专用验证器的自动化通常需要特定于给定程序逻辑的复杂的证明搜索算法,导致有限的工具支持,使得很难对程序逻辑进行实验,例如,在学习,改进或比较它们时。校样大纲检查器填补了这一空白。他们的输入是一个标有最基本证明步骤的程序,就像论文中通常呈现的证明大纲一样。然后,该工具自动检查该大纲是否表示程序逻辑中的有效证明。在本文中,我们系统地开发了一个TaDA逻辑的证明大纲检查器,它将检查简化为一个更简单的验证问题,并且存在自动化工具。我们的方法导致了证明大纲检查器,它比交互式证明器提供了更多的自动化,但是比定制的自动验证器更容易开发。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Formal Methods in System Design

工程技术-计算机:理论方法

CiteScore

2.00

自引率

12.50%

发文量

16

审稿时长

>12 weeks

期刊介绍:

The focus of this journal is on formal methods for designing, implementing, and validating the correctness of hardware (VLSI) and software systems. The stimulus for starting a journal with this goal came from both academia and industry. In both areas, interest in the use of formal methods has increased rapidly during the past few years. The enormous cost and time required to validate new designs has led to the realization that more powerful techniques must be developed. A number of techniques and tools are currently being devised for improving the reliability, and robustness of complex hardware and software systems. While the boundary between the (sub)components of a system that are cast in hardware, firmware, or software continues to blur, the relevant design disciplines and formal methods are maturing rapidly. Consequently, an important (and useful) collection of commonly applicable formal methods are expected to emerge that will strongly influence future design environments and design methods.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: