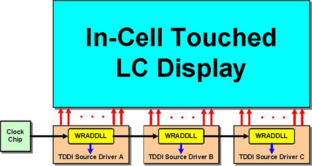

A wide-range and fast-locking all-digital DLL with one-cycle dynamic synchronizing for in-cell touched LC display

Abstract

This paper proposes wide-range and fast locking all-digital delay-locked loop (WRADDLL) circuit with one cycle dynamic synchronizing. The WRADDLL not only synchronizes the input and output clocks in 5 clock cycles but maintains one cycle dynamic locking. The WRADDLL reduces the clock skew between the input and output clocks with three innovative techniques. First, by improving the mirror control circuit, the WRADDLL operates correctly with a flexible duty cycle clock signal. Second, the WRADDLL works precisely and ignores the effect of output load changes by moving the measurement delay line beyond the output driver. Besides, it can achieve one-cycle dynamic locking. Finally, the WRADDLL utilizes the band selector to achieve wide-range operation. After fine tuning, the maximum static phase error is less than 3% of clock cycle. The chip is fabricated by 90 nm standard CMOS process. Its operating frequency range is from 200 MHz to 2 GHz. The power consumption and RMS jitter are 3.24 mW and 1.49 ps at 2 GHz, respectively. The active area of this chip is 0.011 mm2.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: