High efficiency hardware implementation of a ZP-OTFS modulator for next generation high-mobility wireless systems

IF 4.9

3区 计算机科学

Q1 COMPUTER SCIENCE, HARDWARE & ARCHITECTURE

引用次数: 0

Abstract

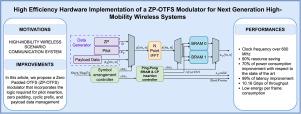

Orthogonal Time Frequency Space (OTFS) is an emerging transmission technology poised to become the dominant paradigm in High-mobility wireless communications and a potential successor to the current Orthogonal Frequency Division Multiplexing (OFDM) technology. In this article, we propose a Zero Padded OTFS (ZP-OTFS) modulator that incorporates the logic required for pilot insertion, zero padding, cyclic prefix, and payload data management. Additionally, the Register Transfer Level (RTL) architecture on Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASIC) will be discussed, with particular focus on the first one. A comparison with state-of-the-art architectures is also conducted to evaluate its performance. The implementation results demonstrate that the proposed architecture offers significant advantages in terms of resource utilization, achieving an improvement percentage up to about 90%, being capable of attaining clock frequencies up to over 600 MHz while maintaining low power consumption. Furthermore, our study explores the relationship between latency, dynamic power consumption, and resource utilization as functions of frame size, proposing design parameters that account for both transmission channel characteristics and hardware constraints, allowing the development of a real OTFS-based transceiver system. Finally, a complete transmission system is presented by integrating the proposed modulator into a complete transmission chain. The transmitted signal is analyzed to validate the effectiveness of the proposed approach.

用于下一代高移动性无线系统的ZP-OTFS调制器的高效硬件实现

正交时频空间(OTFS)是一种新兴的传输技术,有望成为高移动无线通信的主导范式,也是当前正交频分复用(OFDM)技术的潜在继任者。在本文中,我们提出了一个零填充OTFS (ZP-OTFS)调制器,它集成了导频插入、零填充、循环前缀和有效载荷数据管理所需的逻辑。此外,将讨论现场可编程门阵列(fpga)和专用集成电路(ASIC)上的寄存器传输级(RTL)架构,特别关注第一个。还与最先进的架构进行了比较,以评估其性能。实现结果表明,所提出的架构在资源利用率方面具有显著优势,实现了高达90%的改进百分比,能够在保持低功耗的同时实现高达600 MHz以上的时钟频率。此外,我们的研究探讨了延迟、动态功耗和资源利用率之间的关系,并提出了考虑传输信道特性和硬件约束的设计参数,从而允许开发真正的基于otfs的收发器系统。最后,通过将所提出的调制器集成到一个完整的传输链中,给出了一个完整的传输系统。通过对发射信号的分析,验证了该方法的有效性。

本文章由计算机程序翻译,如有差异,请以英文原文为准。

求助全文

约1分钟内获得全文

求助全文

来源期刊

Computers & Electrical Engineering

工程技术-工程:电子与电气

CiteScore

9.20

自引率

7.00%

发文量

661

审稿时长

47 days

期刊介绍:

The impact of computers has nowhere been more revolutionary than in electrical engineering. The design, analysis, and operation of electrical and electronic systems are now dominated by computers, a transformation that has been motivated by the natural ease of interface between computers and electrical systems, and the promise of spectacular improvements in speed and efficiency.

Published since 1973, Computers & Electrical Engineering provides rapid publication of topical research into the integration of computer technology and computational techniques with electrical and electronic systems. The journal publishes papers featuring novel implementations of computers and computational techniques in areas like signal and image processing, high-performance computing, parallel processing, and communications. Special attention will be paid to papers describing innovative architectures, algorithms, and software tools.

求助内容:

求助内容: 应助结果提醒方式:

应助结果提醒方式: